# Integrated Circuits Design by FPGA

مم مم أحمد مؤيد عبدالحسين جامعة الفرات الأوسط التقنية / الكلية التقنية الهندسية / نجف

## Lecture 10

#### **Packages and Components**

## **Objectives of this Lecture**

- To define the new terms **Packages** and **Components**

- To understand the code structure of **Packages** and **Components**.

- To implement examples using Packages and Components.

## **Contents of this Lecture**

Introduction

PACKAGE

- Code structure: library declarations, entity, architecture (Lecture 1)

- VHDL Data Classes and Data Types (Lecture 2)

- VHDL Parallel Code (Lecture 4)

- VHDL Sequential Code (Lecture 5 & Lecture 6)

- Design of Finite State Machines (FSM) (Lecture 8)

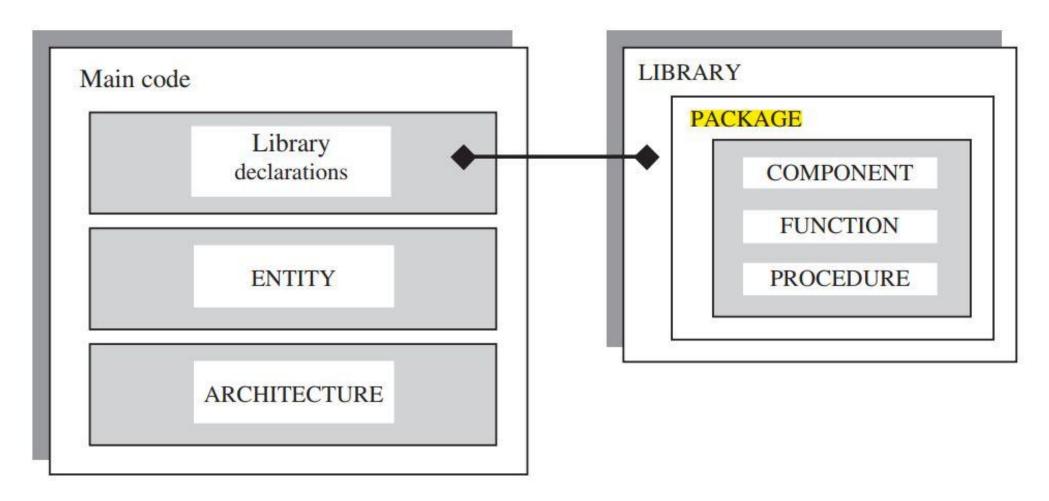

Figure 10.1 Fundamental units of VHDL code.

Packages

Components

Lecture 10 & 11

Functions

Procedures

Lecture 12 & 13

- These new units can be located in the main code itself (that is, on the left-hand side of figure 10.1)

- However, since their main purpose is to allow common pieces of code to be reused and shared, it is more usual to place them in a LIBRARY.

- This also leads to code partitioning, which is helpful when dealing with long codes.

- In summary, frequently used pieces of code can be written in the form of COMPONENTS, FUNCTIONS, or PROCEDURES, then placed in a **PACKAGE**, which is finally compiled into the destination LIBRARY.

- We have already seen that at least two LIBRARIES are generally needed in a design: ieee, and work.

- After studying lectures 10 to 13, we will be able to construct our own libraries, which can then be added to the list above.

• For example, commonly used circuits, like flip-flops, multiplexers, adders, logic gates, etc., can be placed in a LIBRARY, so any project can make use of them without having to explicitly rewrite such codes.

We start by describing the structure of a PACKAGE. Besides COMPONENTS, FUNCTIONS, and PROCEDURES, it can also contain TYPE and CONSTANT definitions, among others. Its syntax is presented below.

```

PACKAGE package_name IS

(declarations)

END package_name;

[PACKAGE BODY package_name IS

(FUNCTION and PROCEDURE descriptions)

END package_name;]

```

As can be seen, the syntax is composed of two parts: <u>PACKAGE</u> and <u>PACKAGE BODY</u>

• The first part (<u>PACKAGE</u>) is mandatory and contains all declarations, while the second part (<u>PACKAGE BODY</u>) is necessary only when one or more subprograms (<u>FUNCTION</u> or <u>PROCEDURE</u>) are declared in the first upper part, in which case it must contain the descriptions (bodies) of the subprograms.

• PACKAGE and PACKAGE BODY must have the same name.

• The declarations list can contain the following: COMPONENT, FUNCTION, PROCEDURE, TYPE, CONSTANT, etc.

#### **Example 10.1: Simple Package**

The example below shows a PACKAGE called my\_package. It contains only TYPE and CONSTANT declarations, so a PACKAGE BODY is not necessary.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

5

PACKAGE my package IS

TYPE state IS (st1, st2, st3, st4);

6

TYPE color IS (red, green, blue);

CONSTANT vec: STD LOGIC VECTOR(7 DOWNTO 0) := "111111111";

END my package;

```

• The next example (example 10.2) contains, besides TYPE and CONSTANT declarations, a <u>FUNCTION</u>. Therefore, a PACKAGE BODY is now needed (details on how to write a FUNCTION will be seen in lecture 12). This function returns TRUE when a positive edge occurs on clk.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

5

PACKAGE my package IS

TYPE state IS (st1, st2, st3, st4);

6

TYPE color IS (red, green, blue);

CONSTANT vec: STD LOGIC VECTOR(7 DOWNTO 0) := "111111111";

8

FUNCTION positive edge(SIGNAL s: STD LOGIC) RETURN BOOLEAN;

10 END my package;

------

12 PACKAGE BODY my package IS

FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN IS

13

BEGIN

14

15

RETURN (s'EVENT AND s='1');

END positive edge;

16

17 END my package;

```

Any of the PACKAGES above (example 10.1 or example 10.2) can now be compiled, becoming then part of our *work* LIBRARY (or any other). To make use of it in a VHDL code, we have to add a new USE clause to the main code (USE work.my package.all), as shown below.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

USE work.my package.all;

ENTITY...

ARCHITECTURE...

. . .

```

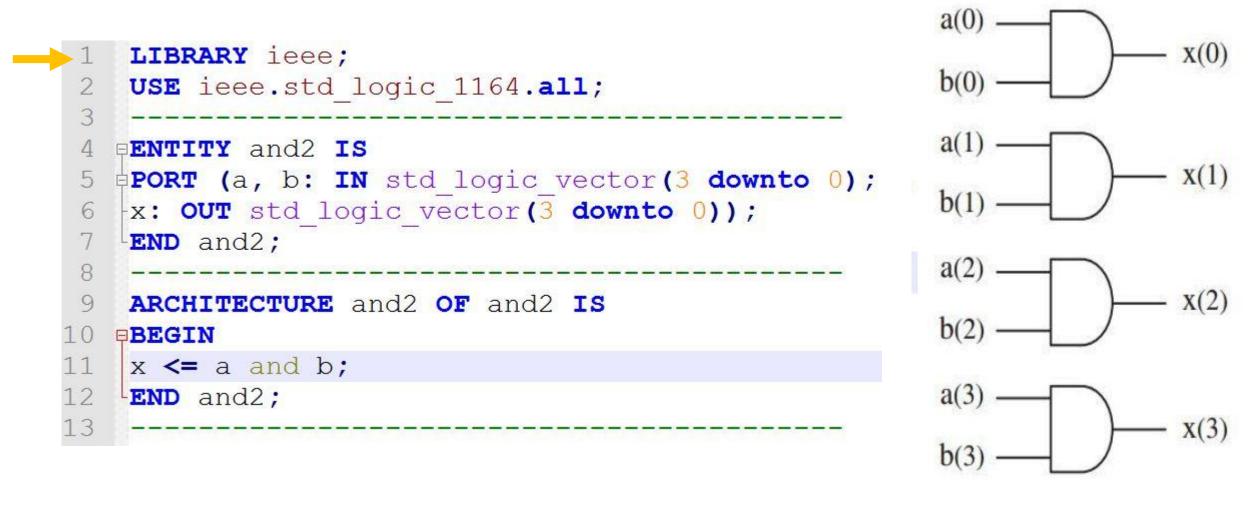

• A **COMPONENT** is simply a piece of conventional code (that is, LIBRARY declarations + ENTITY + ARCHITECTURE, as seen in previous lectures).

• However, by declaring such code as being a **COMPONENT**, it can then be used within another circuit, thus allowing the construction of hierarchical designs.

• A COMPONENT is also another way of partitioning a code and providing code sharing and code reuse.

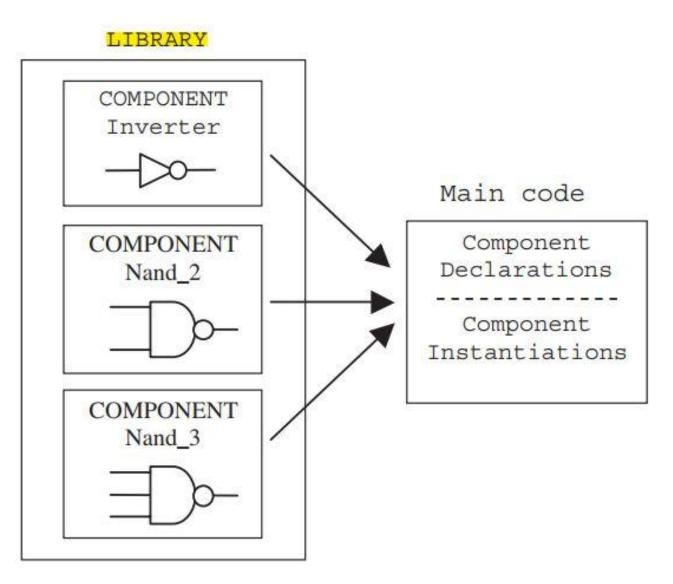

• To use (instantiate) a COMPONENT, it must first be declared. The corresponding syntaxes are shown below.

#### **COMPONENT** declaration:

```

COMPONENT component_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END COMPONENT;

```

#### **COMPONENT** instantiation:

```

label: component_name PORT MAP (port_list);

```

```

---- COMPONENT declaration: -----

COMPONENT inverter IS

PORT (a: IN STD_LOGIC; b: OUT STD_LOGIC);

END COMPONENT;

---- COMPONENT instantiation: -----

U1: inverter PORT MAP (x, y);

```

Figure 10.2 a.: Declarations in the main code itself

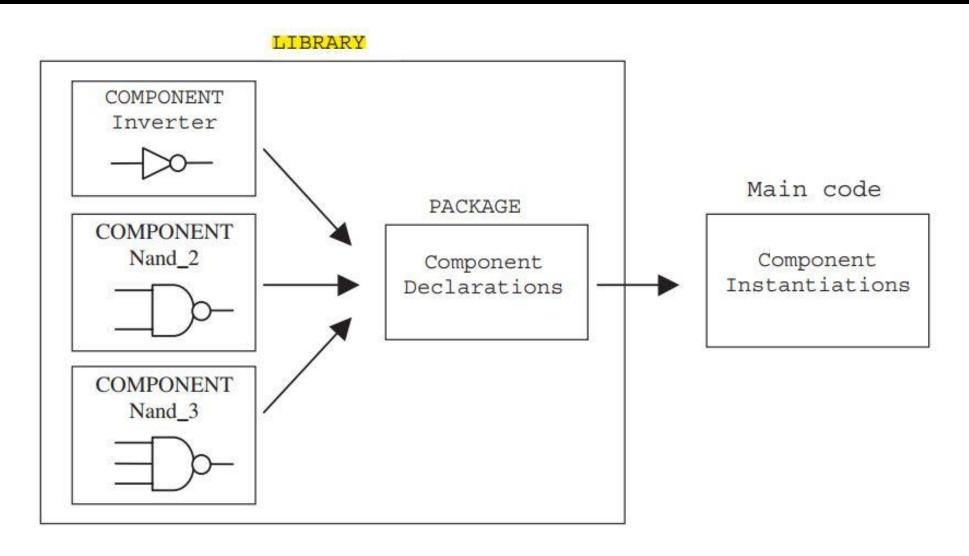

Figure 10.2 b.: Declarations in a PACKAGE

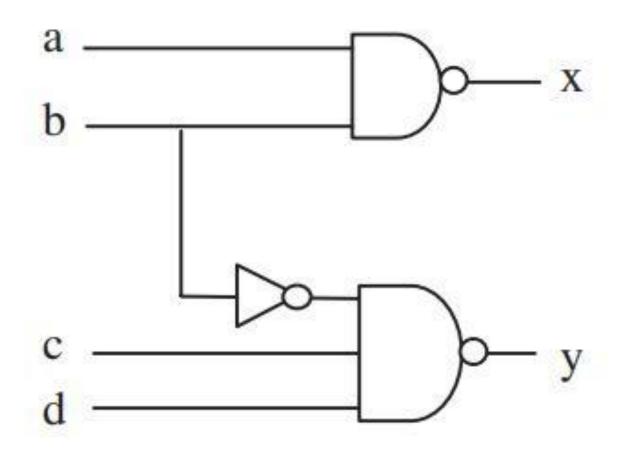

Figure 10.3

Circuit of example 10.3.

#### Components Declared in the Main Code

```

----- File inverter.vhd: -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY inverter IS

PORT (a: IN STD LOGIC; b: OUT STD LOGIC);

END inverter;

ARCHITECTURE inverter OF inverter IS

10 BEGIN

b <= NOT a;

12 END inverter;

13 -----

1 ----- File nand 2.vhd: ------

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY nand 2 IS

PORT (a, b: IN STD LOGIC; c: OUT STD LOGIC);

END nand 2;

ARCHITECTURE nand 2 OF nand 2 IS

10 BEGIN

c <= NOT (a AND b);

12 END nand 2;

13 -----

```

```

---- File nand 3.vhd: -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY nand 3 IS

PORT (a, b, c: IN STD LOGIC; d: OUT STD LOGIC);

END nand 3;

-----

ARCHITECTURE nand 3 OF nand 3 IS

10 BEGIN

d <= NOT (a AND b AND c);

12 END nand 3;

13 -----

---- File project.vhd: -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

_____

ENTITY project IS

PORT (a, b, c, d: IN STD LOGIC;

x, y: OUT STD LOGIC);

END project;

```

#### Components Declared in the Main Code

```

10 ARCHITECTURE structural OF project IS

11

12

COMPONENT inverter IS

13

PORT (a: IN STD LOGIC; b: OUT STD LOGIC);

14

END COMPONENT;

15

-----

16

COMPONENT nand 2 IS

17

PORT (a, b: IN STD LOGIC; c: OUT STD LOGIC);

18

END COMPONENT;

19

______

20

COMPONENT nand 3 IS

21

PORT (a, b, c: IN STD LOGIC; d: OUT STD LOGIC);

22

END COMPONENT;

23

_____

24

SIGNAL W: STD LOGIC;

25 BEGIN

26

U1: inverter PORT MAP (b, w);

U2: nand 2 PORT MAP (a, b, x);

U3: nand 3 PORT MAP (w, c, d, y);

28

29 END structural;

```

#### Components Declared in a Package

```

----- File inverter.vhd: -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY inverter IS

PORT (a: IN STD LOGIC; b: OUT STD LOGIC);

END inverter;

-----

ARCHITECTURE inverter OF inverter IS

10 BEGIN

b <= NOT a;

12 END inverter;

----- File nand 2.vhd: -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY nand 2 IS

PORT (a, b: IN STD LOGIC; c: OUT STD LOGIC);

END nand 2;

ARCHITECTURE nand 2 OF nand 2 IS

10 BEGIN

c <= NOT (a AND b);

12 END nand 2;

13 -----

```

## Components Declared in a Package

```

---- File my components.vhd: ------

LIBRARY ieee;

USE ieee.std logic 1164.all;

PACKAGE my components IS

----- inverter: -----

COMPONENT inverter IS

PORT (a: IN STD LOGIC; b: OUT STD LOGIC);

END COMPONENT;

----- 2-input nand: ---

10

COMPONENT nand 2 IS

11

PORT (a, b: IN STD LOGIC; c: OUT STD LOGIC);

13

END COMPONENT;

---- 3-input nand: ---

14

COMPONENT nand 3 IS

15

16

PORT (a, b, c: IN STD LOGIC; d: OUT STD LOGIC);

17

END COMPONENT;

18

19 END my components;

```

```

1 ---- File project.vhd: -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

USE work.my components.all;

ENTITY project IS

PORT (a, b, c, d: IN STD LOGIC;

8

x, y: OUT STD LOGIC);

END project;

11 ARCHITECTURE structural OF project IS

12

SIGNAL W: STD LOGIC;

13 BEGIN

U1: inverter PORT MAP (b, w);

14

15

U2: nand 2 PORT MAP (a, b, x);

U3: nand 3 PORT MAP (w, c, d, y);

16

17 END structural;

```

# Assignments

• The assignments will be attached to your class room.

# End of lecture 10 Any Questions?