# Integrated Circuits Design by FPGA

م.م. أحمد مؤيد عبدالحسين جامعة الفرات الأوسط التقنية / الكلية التقنية الهندسية / نجف

#### **Packages and Components**

**Arithmetic Logic Unit (ALU)**

### **Objectives of this Lecture**

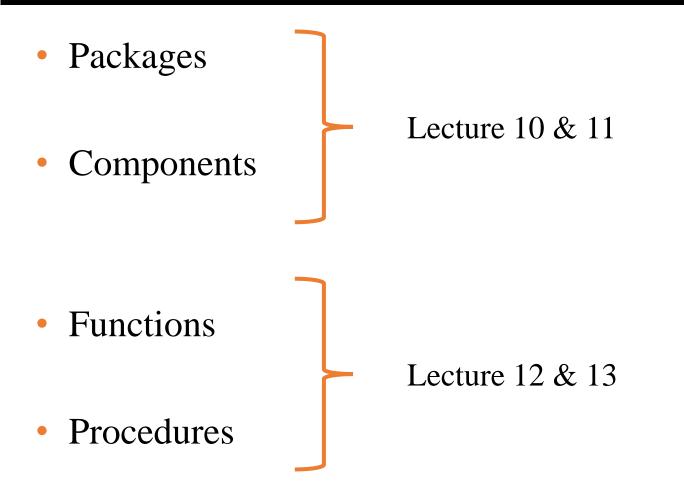

- To review Packages and Components

- To implement ALU example using Components.

## **Contents of this Lecture**

- Introduction (Review)

- PACKAGE (Review)

- COMPONENT (Review)

- ALU Example using COMPONENTS

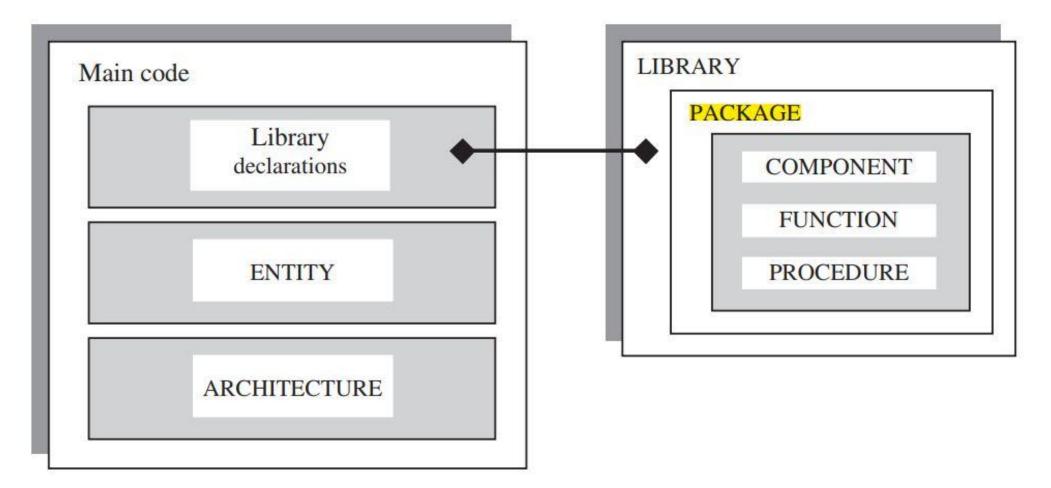

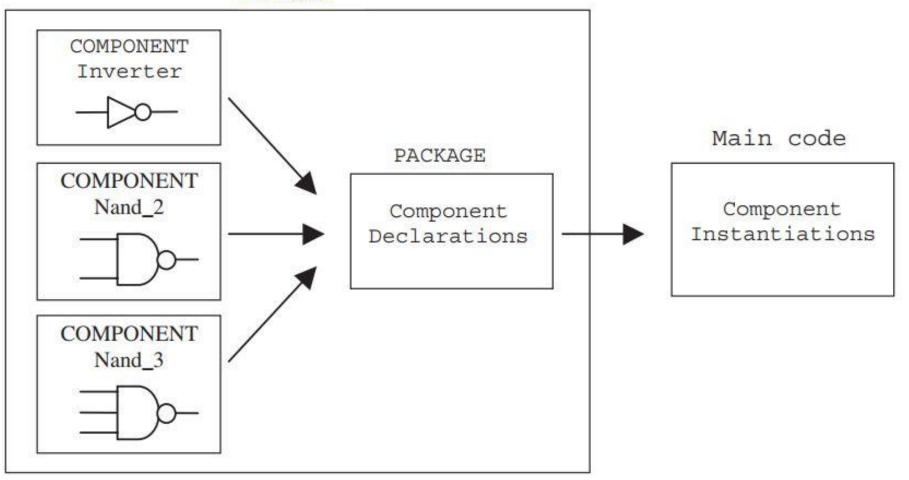

#### Figure 10.1 Fundamental units of VHDL code.

- These new units can be located in the main code itself (that is, on the lefthand side of figure 10.1)

- However, since their main purpose is to allow common pieces of code to be reused and shared, it is more usual to place them in a LIBRARY.

- This also leads to code partitioning, which is helpful when dealing with long codes.

- In summary, frequently used pieces of code can be written in the form of COMPONENTS, FUNCTIONS, or PROCEDURES, then placed in a **PACKAGE**, which is finally compiled into the destination LIBRARY.

- We have already seen that at least two LIBRARIES are generally needed in a design: **ieee**, and **work**.

- After studying lectures 10 to 13, we will be able to construct our own libraries, which can then be added to the list above.

• For example, commonly used circuits, like flip-flops, multiplexers, adders, logic gates, etc., can be placed in a LIBRARY, so any project can make use of them without having to explicitly rewrite such codes.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

2

3

ENTITY and 2 IS

PORT (a, b: IN std logic vector (3 downto 0);

5

x: OUT std logic vector (3 downto 0));

6

END and2;

_____

8

ARCHITECTURE and2 OF and2 IS

9

BEGIN

10

x \leq a and b;

END and2;

12

13

```

We start by describing the structure of a **PACKAGE**. Besides COMPONENTS, FUNCTIONS, and PROCEDURES, it can also contain **TYPE and CONSTANT** definitions, among others. Its syntax is presented below.

```

PACKAGE package_name IS

(declarations)

END package_name;

[PACKAGE BODY package_name IS

(FUNCTION and PROCEDURE descriptions)

END package_name;]

```

As can be seen, the syntax is composed of two parts: <u>PACKAGE</u> and <u>PACKAGE BODY</u>

• The first part (<u>PACKAGE</u>) is mandatory and contains all declarations, while the second part (<u>PACKAGE BODY</u>) is necessary only when one or more subprograms (FUNCTION or PROCEDURE) are declared in the first upper part, in which case it must contain the descriptions (bodies) of the subprograms.

• PACKAGE and PACKAGE BODY must have the same name.

• The declarations list can contain the following: COMPONENT, FUNCTION, PROCEDURE, TYPE, CONSTANT, etc.

#### Example 10.1: Simple Package

The example below shows a PACKAGE called my\_package. It contains only TYPE and CONSTANT declarations, so a PACKAGE BODY is not necessary.

```

1

LIBRARY ieee;

2

USE ieee.std logic 1164.all;

3

4

5

PACKAGE my package IS

TYPE state IS (st1, st2, st3, st4);

6

7

TYPE color IS (red, green, blue);

CONSTANT vec: STD LOGIC VECTOR(7 DOWNTO 0) := "11111111";

8

END my package;

9

10

```

• The next example (example 10.2) contains, besides TYPE and CONSTANT declarations, a <u>FUNCTION</u>. Therefore, a PACKAGE BODY is now needed (details on how to write a FUNCTION will be seen in lecture 12). This function returns TRUE when a positive edge occurs on clk.

```

LIBRARY ieee;

2

USE ieee.std_logic_1164.all;

3

4

5

PACKAGE my package IS

TYPE state IS (st1, st2, st3, st4);

6

7

TYPE color IS (red, green, blue);

CONSTANT vec: STD LOGIC VECTOR(7 DOWNTO 0) := "11111111";

8

FUNCTION positive edge(SIGNAL s: STD LOGIC) RETURN BOOLEAN;

9

10 END my package;

11

_______

12 PACKAGE BODY my package IS

FUNCTION positive_edge(SIGNAL s: STD_LOGIC) RETURN BOOLEAN IS

13

BEGIN

14

15

RETURN (S'EVENT AND S='1');

END positive edge;

16

17 END my package;

18

_______

```

Any of the PACKAGES above (example 10.1 or example 10.2) can now be compiled, becoming then part of our *work* LIBRARY (or any other). To make use of it in a VHDL code, we have to add a new USE clause to the main code (USE work.my\_package.all), as shown below.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.my_package.all;

ENTITY...

ARCHITECTURE...

```

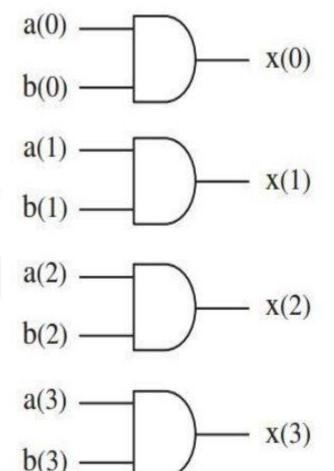

• A **COMPONENT** is simply a piece of conventional code (that is, LIBRARY declarations + ENTITY + ARCHITECTURE, as seen in previous lectures).

• However, by declaring such code as being a **COMPONENT**, it can then be used within another circuit, thus allowing the construction of hierarchical designs.

• A **COMPONENT** is also another way of partitioning a code and providing code sharing and code reuse.

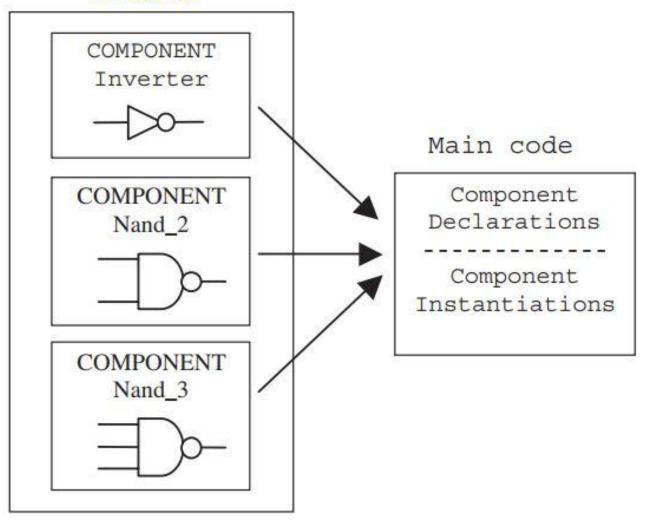

• To use (instantiate) a COMPONENT, it must first be declared. The corresponding syntaxes are shown below.

**COMPONENT** declaration:

```

COMPONENT component_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END COMPONENT;

```

**COMPONENT** instantiation:

label: component name PORT MAP (port list);

----- COMPONENT declaration: -----COMPONENT inverter IS PORT (a: IN STD\_LOGIC; b: OUT STD\_LOGIC); END COMPONENT;

----- COMPONENT instantiation: ------

U1: inverter PORT MAP (x, y);

#### LIBRARY

Figure 10.2 a. : Declarations in the main code itself

#### LIBRARY

Figure 10.2 b. : Declarations in a PACKAGE

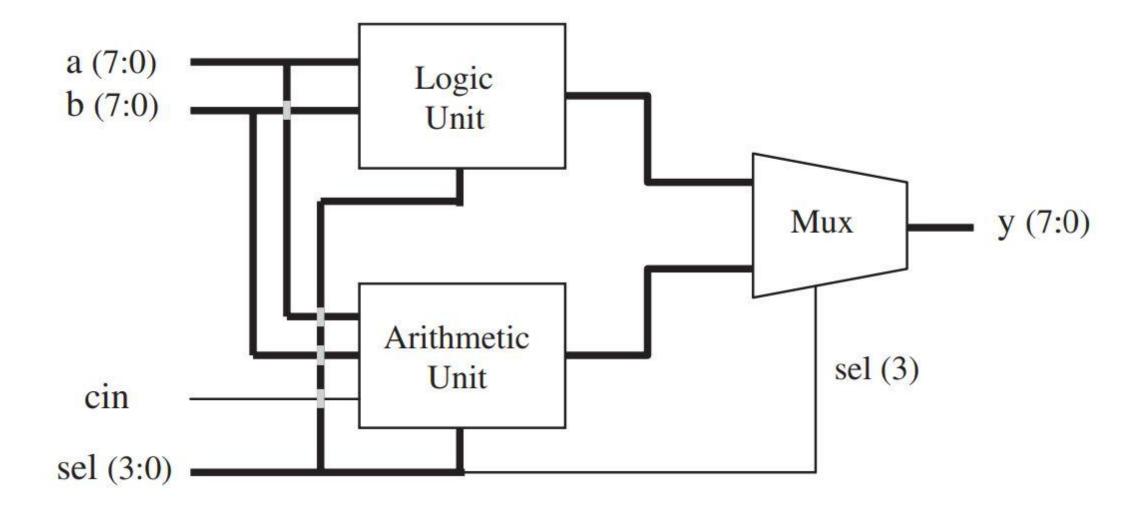

| sel  | Operation     | Function               | Unit       |

|------|---------------|------------------------|------------|

| 0000 | y <= a        | Transfer a             |            |

| 0001 | y <= a+1      | Increment a            |            |

| 0010 | y <= a-1      | Decrement a            |            |

| 0011 | y <= b        | Transfer b             | Arithmetic |

| 0100 | y <= b+1      | Increment b            |            |

| 0101 | y <= b-1      | Decrement b            |            |

| 0110 | y <= a+b      | Add a and b            |            |

| 0111 | y <= a+b+cin  | Add a and b with carry |            |

| 1000 | y <= NOT a    | Complement a           |            |

| 1001 | y <= NOT b    | Complement b           |            |

| 1010 | y <= a AND b  | AND                    |            |

| 1011 | y <= a OR b   | OR                     | Logic      |

| 1100 | y <= a NAND b | NAND                   |            |

| 1101 | y <= a NOR b  | NOR                    |            |

| 1110 | y <= a XOR b  | XOR                    |            |

| 1111 | y <= a XNOR b | XNOR                   |            |

#### تنفيذ مباشر في فايل واحد ALU

| 2  | LIBRARY ieee;                                       | 23       | b-1 WHEN "101",                             |

|----|-----------------------------------------------------|----------|---------------------------------------------|

| 3  | USE ieee.std_logic_1164.all;                        | 24       | a+b WHEN "110",                             |

| 4  | USE <pre>ieee.std_logic_unsigned.all;</pre>         | 25       | a+b+cin WHEN OTHERS;                        |

| 5  |                                                     | 01303508 |                                             |

| 6  | ENTITY ALU IS                                       | 26       | Logic unit:                                 |

| 7  | PORT (a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0);       | 27       | WITH sel(2 DOWNTO 0) SELECT                 |

| 8  | sel: IN STD_LOGIC_VECTOR (3 DOWNTO 0);              | 28       | logic <= NOT a WHEN "000",                  |

| 9  | cin: IN STD_LOGIC;                                  | 29       | NOT b WHEN "001",                           |

| 10 | y: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));              | 30       | a AND b WHEN "010",                         |

| 11 | END ALU;                                            | 31       | a OR b WHEN "011",                          |

| 12 |                                                     | 32       | a NAND b WHEN "100",                        |

| 13 | ARCHITECTURE dataflow OF ALU IS                     | 33       | a NOR b WHEN "101",                         |

| 14 | SIGNAL arith, logic: STD_LOGIC_VECTOR (7 DOWNTO 0); | 105 08   | anni-series 20 december 20 accession and 20 |

| 15 | BEGIN                                               | 34       | a XOR b WHEN "110",                         |

| 16 |                                                     | 35       | NOT (a XOR b) WHEN OTHERS;                  |

| 17 | WITH sel(2 DOWNTO 0) SELECT                         | 36       | Mux:                                        |

| 18 | arith <= a WHEN "000",                              | 37       | WITH sel(3) SELECT                          |

| 19 | a+1 WHEN "001",                                     | 38       | y <= arith WHEN '0',                        |

| 20 | a-1 WHEN "010",                                     | 39       | logic WHEN OTHERS;                          |

| 21 | b WHEN "011",                                       | 40       | END dataflow;                               |

| 22 | b+1 WHEN "100",                                     | 41       |                                             |

| 1  |                                                     |          |                                             |

| 1 COMPONENT arith_unit:                                |                                                  |

|--------------------------------------------------------|--------------------------------------------------|

| 2 LIBRARY ieee;                                        | 1 COMPONENT logic_unit:                          |

| 3 USE ieee.std_logic_1164.all;                         | 2 LIBRARY ieee;                                  |

| 4 USE ieee.std_logic_unsigned.all;                     | 3 USE ieee.std_logic_1164.all;                   |

| 5                                                      | 4                                                |

| 6 ENTITY arith unit IS                                 | 5 ENTITY logic_unit IS                           |

|                                                        | 6 PORT ( a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0); |

| 7 PORT ( a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0);       | 7 sel: IN STD_LOGIC_VECTOR (2 DOWNTO 0);         |

| 8 sel: IN STD_LOGIC_VECTOR (2 DOWNTO 0);               | 8 x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));         |

| <pre>9 cin: IN STD_LOGIC;</pre>                        | 9 END logic_unit;                                |

| <pre>10 x: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));</pre>   | 10                                               |

| 11 END arith_unit;                                     | 11 ARCHITECTURE logic_unit OF logic_unit IS      |

| 12                                                     | 12 BEGIN                                         |

| 13 ARCHITECTURE arith_unit OF arith_unit IS            | 13 WITH sel SELECT                               |

| 14 SIGNAL arith, logic: STD_LOGIC_VECTOR (7 DOWNTO 0); | 14 $x \le NOT a WHEN "000",$                     |

| 15 BEGIN                                               | 15 NOT b WHEN "001",                             |

| 16 WITH sel SELECT                                     | 16 a AND b WHEN "010",                           |

| 17 x <= a WHEN "000",                                  | 17 a OR b WHEN "011",                            |

| 18 a+1 WHEN "001",                                     |                                                  |

| 19 a-1 WHEN "010",                                     | 18 a NAND b WHEN "100",                          |

| 20 b WHEN "011",                                       | 19 a NOR b WHEN "101",                           |

| 21 b+1 WHEN "100",                                     | 20 a XOR b WHEN "110",                           |

| 22 b-1 WHEN "101",                                     | 21 NOT (a XOR b) WHEN OTHERS;                    |

| 23 a+b WHEN "110",                                     | 22 END logic unit;                               |

| 24 a+b+cin WHEN OTHERS;                                | <b>23</b> <sub>23</sub>                          |

| 25 END arith_unit;<br>26                               |                                                  |

| 20                                                     |                                                  |

```

----- COMPONENT mux: ------

LIBRARY ieee;

2

USE ieee.std_logic_1164.all;

3

4

ENTITY mux IS

5

6

PORT ( a, b: IN STD LOGIC VECTOR (7 DOWNTO 0);

7

sel: IN STD LOGIC;

8

x: OUT STD LOGIC VECTOR (7 DOWNTO 0));

9

END mux;

11 ARCHITECTURE mux OF mux IS

12 BEGIN

13 WITH sel SELECT

14 x <= a WHEN '0',

15

b WHEN OTHERS;

16 END mux;

17

```

| 1   | Project ALU (main code):                                 |       |                                                           |  |

|-----|----------------------------------------------------------|-------|-----------------------------------------------------------|--|

| 2   | LIBRARY ieee;                                            | 21    | COMPONENT logic_unit IS                                   |  |

| 3   | USE ieee.std logic 1164.all;                             | 22    | PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0);             |  |

| 4   |                                                          | 23    | <pre>sel: IN STD_LOGIC_VECTOR(2 DOWNTO 0);</pre>          |  |

| 5   | ENTITY alu IS                                            | 24    | <pre>x: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));</pre>          |  |

| 6   | PORT ( a, b: IN STD LOGIC VECTOR(7 DOWNTO 0);            | 25    | END COMPONENT;                                            |  |

| 7   |                                                          | 26    |                                                           |  |

|     | cin: IN STD_LOGIC;                                       | 27    | COMPONENT MUX IS                                          |  |

| 8   | <pre>sel: IN STD_LOGIC_VECTOR(3 DOWNTO 0);</pre>         | 28    | <pre>PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0);</pre>  |  |

| 9   | y: OUT STD LOGIC VECTOR(7 DOWNTO 0));                    | 29    | sel: IN STD_LOGIC;                                        |  |

| 1.0 |                                                          | 30    | <pre>x: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));</pre>          |  |

| 10  | END alu;                                                 | 31    | END COMPONENT;                                            |  |

| 11  |                                                          | 32    |                                                           |  |

| 12  | ARCHITECTURE alu OF alu IS                               | 33    | SIGNAL x1, x2: STD_LOGIC_VECTOR(7 DOWNTO 0);              |  |

| 13  |                                                          | 34    |                                                           |  |

| 14  | COMPONENT arith unit IS                                  | 35 BE | GIN                                                       |  |

|     |                                                          | 36    | U1: arith_unit PORT MAP (a, b, cin, sel(2 DOWNTO 0), x1); |  |

| 15  | <pre>PORT ( a, b: IN STD_LOGIC_VECTOR(7 DOWNTO 0);</pre> | 37    | U2: logic_unit PORT MAP (a, b, sel(2 DOWNTO 0), x2);      |  |

| 16  | cin: IN STD_LOGIC;                                       | 38    | U3: mux PORT MAP (x1, x2, sel(3), y);                     |  |

| 17  | <pre>sel: IN STD_LOGIC_VECTOR(2 DOWNTO 0);</pre>         | 39 EN | ID alu;                                                   |  |

| 18  | <pre>x: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));</pre>         |       |                                                           |  |

| 19  | END COMPONENT;                                           |       |                                                           |  |

| 20  |                                                          |       |                                                           |  |

|     |                                                          |       |                                                           |  |

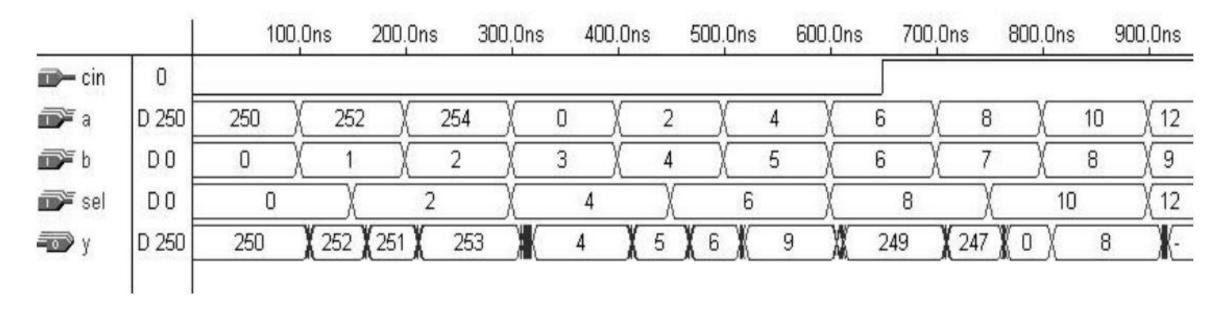

Figure 10.8 Simulation results of example 10.6.

• The assignments will be attached to your class room.

End of lecture 11 Any Questions ?