# Integrated Circuits Design by FPGA

مم مم أحمد مؤيد عبدالحسين جامعة الفرات الأوسط التقنية / الكلية التقنية الهندسية / نجف

## Lecture 3

#### Lecture 3:

Part 1: Using the FPGA board

# Objectives of this Lecture

■ To learn how to implement a design on an FPGA board.

# Contents of this Lecture

Implementation of a Shift Register design on an FPGA board.

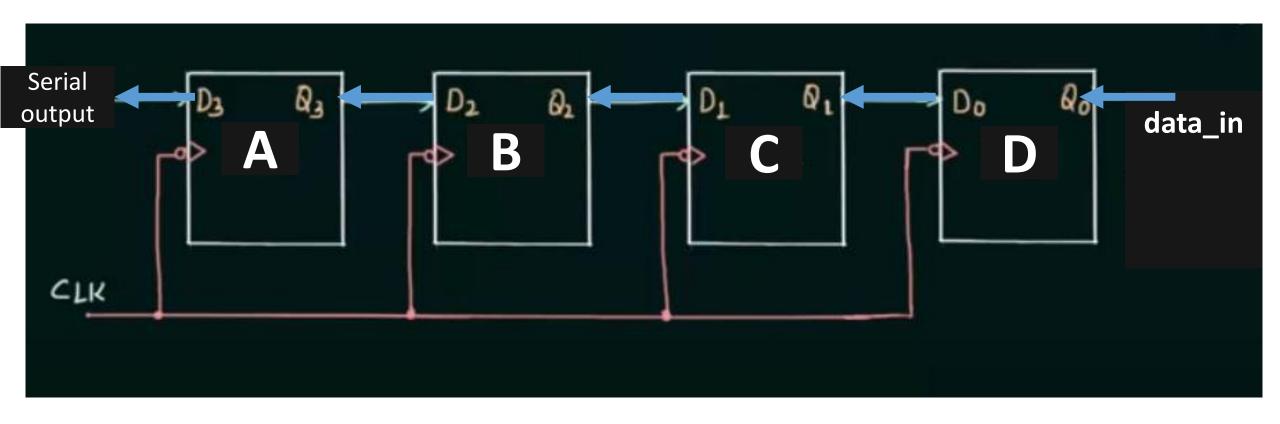

#### Implementation of a Shift Register on FPGA board

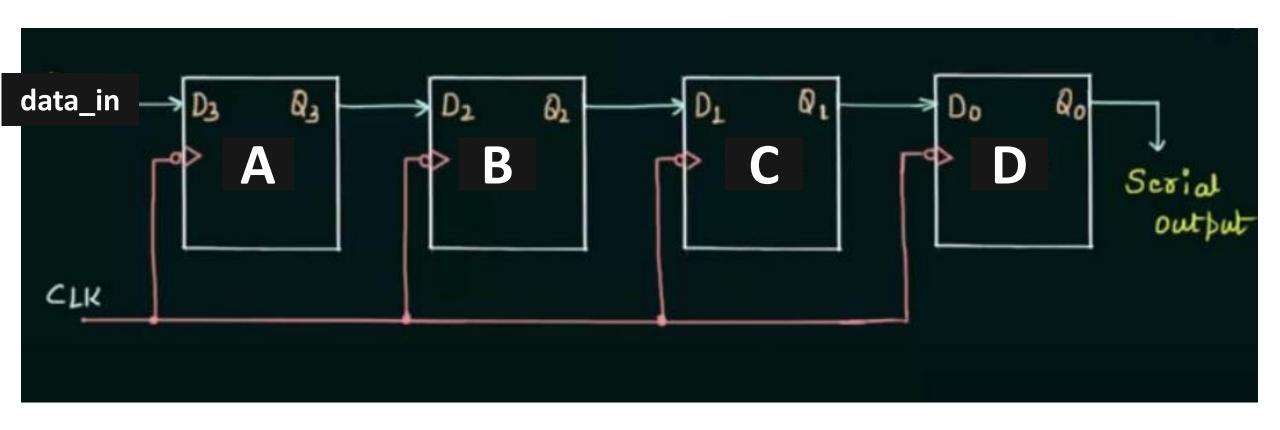

- Shift Registers are used for data storage or for the movement of data.

- Therefore commonly used inside calculators or computers to store data as binary numbers.

- Convert the data from either a serial to parallel or parallel to serial format.

What is a shift register?

#### Implementation of a Shift Register on FPGA board

```

-- Library's

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use IEEE.numeric std.all;

-- Entity Declaration

⊟entity Shift Req is

port (

-- single bit in register

: out std logic;

: out std logic;

-- single bit in register

10

: out std logic;

-- single bit in register

: out std logic;

-- single bit in register

data in

: in std logic; -- data input (1 or 0)

reset

: in std logic;

-- when this signal goes high clear

-- all bit values on a clock cycle

clk

: in std logic);

-- input clock

end Shift Reg;

-- Architecture Body

□architecture behavior of Shift Reg is

-- Defined Signals used in Architecture

signal A reg, B_reg : std_logic := '0';

signal C req, D req : std logic := '0';

```

```

--- Begin Architecture

begin

28

29

-- Signal Assignments

A <= A reg;

B <= B reg;

C <= C rea:

D <= D reg;

-- Process that is used to shift values

** HINT **

-- (We want this process to be evaluated

-- on every clock cycle)

reg process: process(clk)

begin

41

if (rising edge (clk)) then

if(reset = '1') then

A reg <= '0';

B reg <= '0';

C req <= '0';

46

D reg <= '0';

else

** HINT **

49

-- This is where the shifting actually occurs

50

-- depending on how you code this, you can have

51

-- a shift right or shift left register

52

A reg <= data in;

53

B reg <= A reg;

54

C reg <= B reg;

55

D reg <= C reg;

56

end if;

end if;

57

58

end process reg process;

end behavior:

```

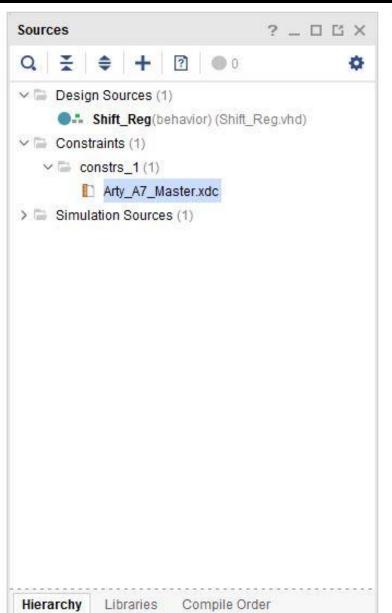

#### Implementation of a Shift Register on FPGA board

```

Project Summary

Arty A7 Master.xdc

? 母 [

D:/Users/dell/Vivado_projects/Shift_Register/Shift_Register.srcs/constrs_1/imports/Research tools/Arty_A7_Master.xdc

-dict {PACKAGE PIN A8 IOSTANDARD LVCMOS33} [get ports data in]

-dict (PACKAGE PIN C11 IOSTANDARD LVCMOS33) [get ports (sv[0])]

#set property -dict (PACKAGE PIN C10 IOSTANDARD LVCMOS33)

#set property -dict {PACKAGE PIN A10 IOSTANDARD LVCMOS33}

20

##RGB LEDs

#set property -dict

PACKAGE PIN E1

[get ports { led0 b }]; #IO L18N T2

#set property -dict

PACKAGE PIN F6

get ports

{ led0 g }]; #IO L19N T3

#set property -dict

PACKAGE PIN G6

[get ports (

led0 r }]; #IO L19P T3

PACKAGE PIN G4

#set property -dict

[get ports { led1 b }]; #IO L20P T3

IOSTANDARD LVCMOS33 } [get ports { led1 g }]; #IO L21P T3

PACKAGE PIN J4

#set property -dict

#set property -dict {

PACKAGE PIN G3

[get ports { led1 r }]; #IO L20N T3

PACKAGE PIN H4

[get ports { led2 b }]; #IO L21N T3

#set property -dict (

PACKAGE PIN J2

#set property -dict

[get ports ( led2 g )]; #IO L22N T3

#set property -dict

PACKAGE PIN J3

[get ports { led2 r }]; #IO L22P T3

#set property -dict

PACKAGE PIN K2

get ports { led3 b }]; #IO L23P T3

#set property -dict

PACKAGE PIN H6

[get ports { led3 g }]; #IO L24P T3

#set property -dict

PACKAGE PIN K1

[get ports { led3 r }]; #IO L23N T3

35

##LEDs

36

37

PACKAGE PIN H5

[get ports A]; #IO L24N T3 35 Sch=led

set property -dict {

IOSTANDARD LVCMOS33

PACKAGE PIN J5

set property -dict {

IOSTANDARD LVCMOS33

[get ports B]; #IO 25 35 Sch=led[5]

PACKAGE PIN T9

[get ports C]; #IO L24P T3 A01 D17 1

set property -dict

PACKAGE PIN T10

IOSTANDARD LVCMOS33 } [get ports D]; #IO L24N T3 A00 D16 1 ~

set property -dict {

```

## Lecture 3

Lecture 3:

Part 2: VHDL Test Bench

# **Objectives of this Lecture**

- To define and introduce a basic Test Bench.

- To learn how to construct a Test Bench.

### **Contents of this Lecture**

- What is a Test Bench?

- Test Bench Outline

- Shift Register Example

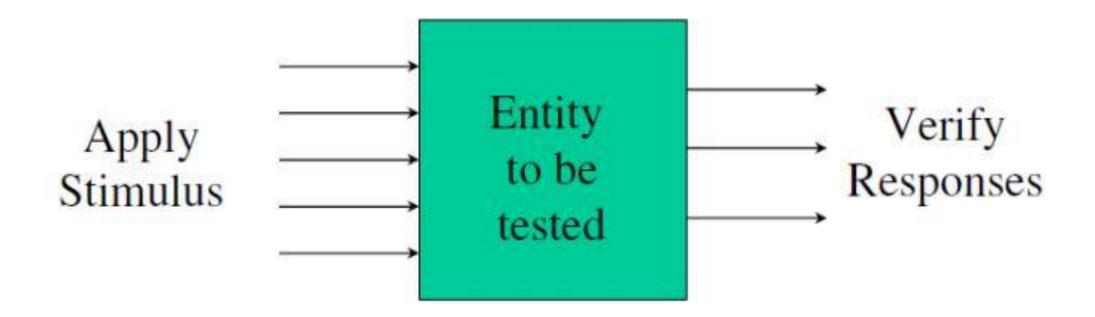

#### What is a Test Bench?

• A test bench model is used to exercise and verify that your VHDL design is working correctly as expected.

• A test bench **cannot** be synthesized and placed onto an FPGA board.

• You can code the test benches using Notepad++, or Vivado IDE.

Vivado IDE is used to execute the simulation.

#### What is a Test Bench?

- Test Benches consist of:

- Entity

- Contains no ports or generics

- Architecture

- Declares, instantiates, and wires together the driver model and the model under test

- The driver model provides stimulus and verifies the response of the model under test

## What is a Test Bench?

#### **Test Bench Outline**

```

-- Architecture

--Libraries

marchitecture testing of Test Bench name is

□-- intantiate component of the VHDL entity you

library IEEE;

--- are testing

component LFSR3

use IEEE.STD LOGIC 1164.ALL;

port (

clk : in STD LOGIC;

use IEEE.numeric std.all;

outp: out STD LOGIC VECTOR ( 2 downto 0 ));

24

end component;

26

6 p--these two libraries are only

-- Simulation signals

: std logic := '0';

signal clk sim

--supprtted in Test Bench (these

: std logic vector(2 downto 0);

signal outp sim

--two libraries will not be

31

begin

-- Sometimes this is called UUT (Unit Under Test)

9 1-- synthesized)

dev to test: LFSR3

10 use std.textio.all;

34

port map (clk sim, outp sim);

35

use ieee.std logic textio.all ;

36

-- Simulate the input clock to your design

clk proc : process

38

begin

wait for 50 ns;

-- Entity

40

clk sim <= not clk sim;

end process clk proc;

pentity Test Bench name is

15 end;

end testing;

```

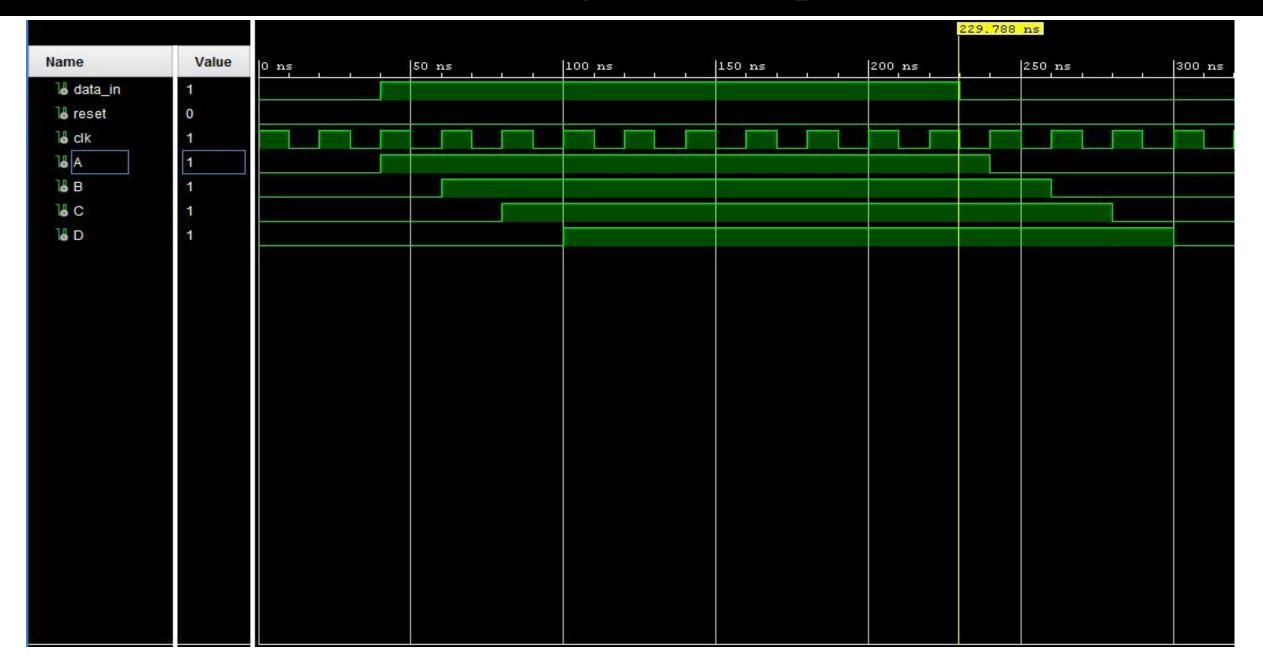

#### Shift Register Example

#### **Shift Register Example**

```

25

library IEEE;

26

use IEEE.STD LOGIC 1164.ALL;

use IEEE.numeric std.all;

27

28

entity test Shift Reg is

29

end;

30

parchitecture test of test Shift Reg is

32

component Shift Req

port (A: out std logic;

33

B: out std_logic;

34

C: out std logic;

13

out std_logic;

14

D:

35

data in: in std logic;

15

36

in std logic;

16

reset:

37

17

clk:

in std logic);

end component;

18

38

19

39

signal data in : std logic := '0';

20

signal reset : std logic := '0';

40

21

signal clk : std logic := '1';

22

41

23

signal A, B, C, D: std logic;

42

24

43

```

```

begin

dev to test: shift req

port map (A, B, C, D, data in, reset, clk);

clk stimulus: process

begin

wait for 10 ns;

clk <= not clk;

end process clk stimulus;

data stimulus: process

begin

wait for 40 ns;

data in <= not data in;

wait for 150 ns;

end process data stimulus;

end test;

```

#### Shift Register Example

# Assignment

• For the same VHDL code of shift register in this lecture. How you can make the shifting process in the **left** direction?

# End of lecture 3

Any Questions?