# Integrated Circuits Design by FPGA

مم مم أحمد مؤيد عبدالحسين جامعة الفرات الأوسط التقنية / الكلية التقنية الهندسية / نجف

### Lecture 4

#### **VHDL Parallel Code**

### Lecture 4

**Parallel** ≡ Concurrent

### **Objectives of this Lecture**

- To understand what is the Parallel (Concurrent) VHDL code.

- This lecture is very important, for it allows a better understanding of where the parallel VHDL code or sequential VHDL code, as well as the consequences of using one or the other.

#### Contents of this Lecture

- Introduction about Parallel VHDL code.

- Parallel VHDL code using Operators .

- Parallel VHDL code using WHEN.

- Parallel VHDL code using **GENERATE**.

#### Introduction about Parallel VHDL code

- VHDL code can be concurrent (parallel) or sequential.

- The concurrent statements in VHDL are **WHEN** and **GENERATE**. Besides them, assignments using only operators (**AND**, **NOT**, +, \*, etc.) can also be used to construct concurrent code.

- VHDL code is inherently concurrent (parallel). Only statements placed <u>inside</u> a **PROCESS**, **FUNCTION**, or **PROCEDURE** are sequential. Still, though within these blocks the execution is sequential, the block, as a whole, is concurrent with any other (external) statements.

- concurrent code only can be used <u>outside</u> **PROCESSES**, **FUNCTIONS**, or **PROCEDURE**.

Operators

Logical: AND, OR, NOT, XOR, XNOR, ...

Mathematical: +

\_ \* /

#### Example 5.1

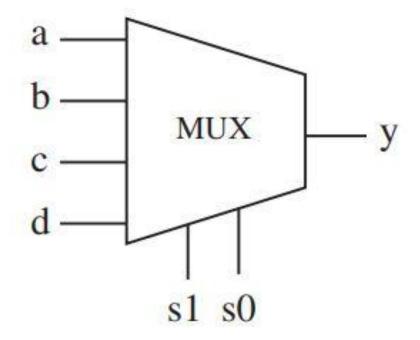

Figure 5.3 Multiplexer of example 5.1.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY mux IS

PORT (a, b, c, d, s0, s1: IN STD LOGIC;

y: OUT STD LOGIC);

END mux;

povallel

10 ARCHITECTURE pure logic OF mux IS

11 BEGIN

y <= (a AND NOT s1 AND NOT s0) OR

12

13

(b AND NOT s1 AND s0) OR

14

(c AND s1 AND NOT s0) OR

15

(d AND s1 AND s0);

16 END pure logic;

```

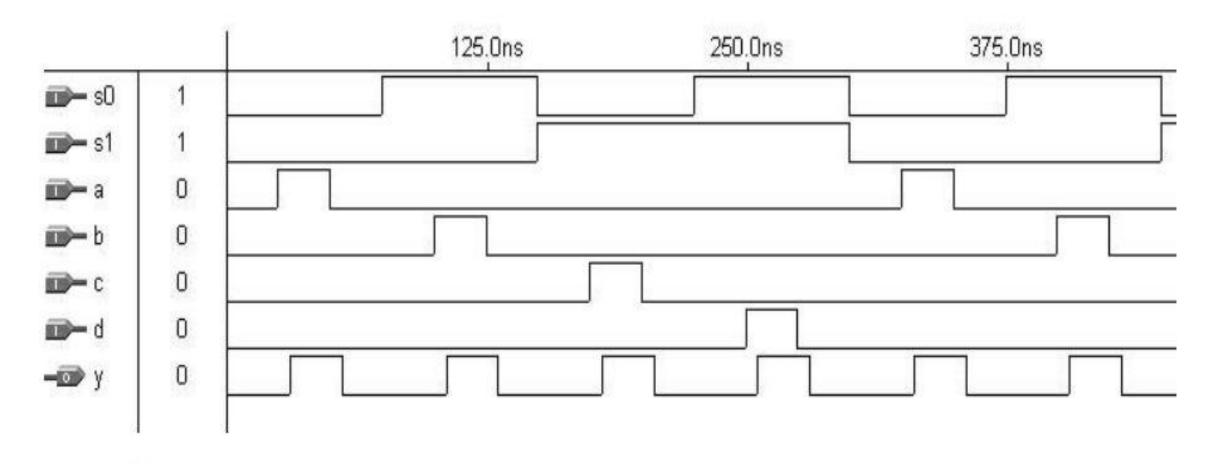

Figure 5.4 Simulation results of example 5.1.

Multiplexer

• As mentioned above, WHEN is one of the fundamental concurrent statements (along with operators and GENERATE).

• It appears in two forms: WHEN / ELSE (simple WHEN) and WITH/SELECT / WHEN (selected WHEN).

#### WHEN / ELSE:

```

assignment WHEN condition ELSE assignment WHEN condition ELSE ...;

```

#### WITH / SELECT / WHEN:

```

WITH identifier SELECT assignment WHEN value, assignment WHEN value, ...;

```

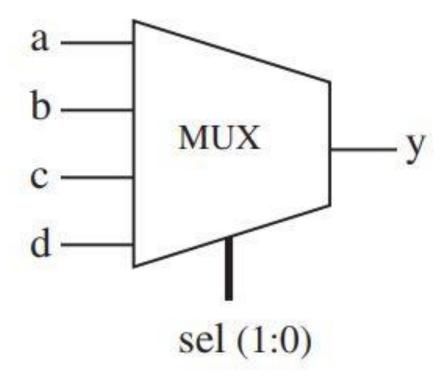

#### Example 5.2

Figure 5.5 Multiplexer of example 5.2.

```

----- Solution 1: with WHEN/ELSE -----

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY mux IS

PORT (a, b, c, d: IN STD LOGIC;

sel: IN STD LOGIC VECTOR (1 DOWNTO 0);

y: OUT STD LOGIC);

END mux;

11 ARCHITECTURE mux1 OF mux IS

12 BEGIN

13

y <= a WHEN sel="00" ELSE

b WHEN sel="01" ELSE

14

Parallel code

15

c WHEN sel="10" ELSE

16

d;

17 END mux1;

```

```

--- Solution 2: with WITH/SELECT/WHEN ----

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY mux IS

PORT ( a, b, c, d: IN STD LOGIC;

sel: IN STD LOGIC VECTOR (1 DOWNTO 0);

y: OUT STD LOGIC);

END mux;

11 ARCHITECTURE mux2 OF mux IS

12 BEGIN

13

WITH sel SELECT

14 y <= a WHEN "00", -- notice "," instead of ";"</pre>

b WHEN "01",

15

Parallel code

16

c WHEN "10",

17

d WHEN OTHERS;

18 END mux2;

15

```

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY mux IS

PORT ( a, b, c, d: IN STD LOGIC;

6

sel: IN INTEGER RANGE 0 TO 3;

y: OUT STD LOGIC);

END mux;

10 ---- Solution 1: with WHEN/ELSE -----

11 ARCHITECTURE mux1 OF mux IS

12 BEGIN

y <= a WHEN sel=0 ELSE

13

14

b WHEN sel=1 ELSE

15

c WHEN sel=2 ELSE

16

d;

17 END mux1;

```

```

18 -- Solution 2: with WITH/SELECT/WHEN

19 ARCHITECTURE mux2 OF mux IS

20 BEGIN

21

WITH sel SELECT

y \le a WHEN 0,

22

23

b WHEN 1,

24

c WHEN 2,

25

d WHEN 3;

-- here, 3 or OTHERS are equivalent,

26 END mux2;

-- for all options are tested anyway

```

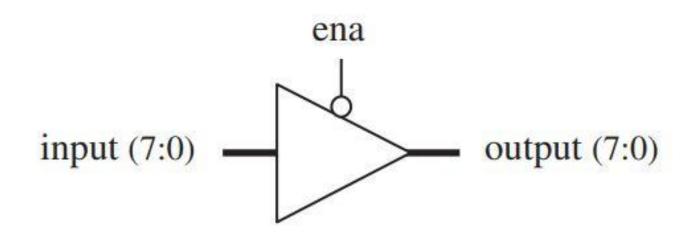

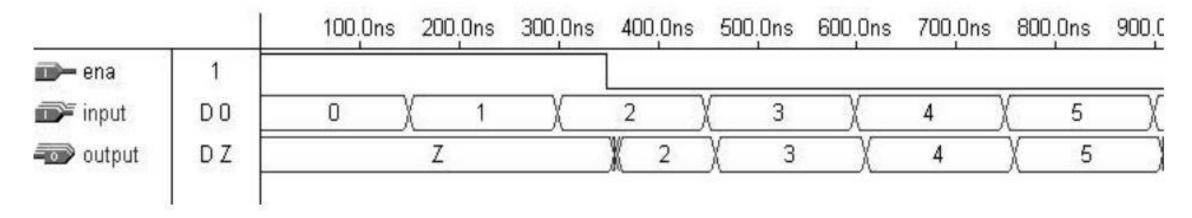

Figure 5.6

Tri-state buffer of example 5.3.

**Example 5.3: Tri-state Buffer**

output = input when ena (enable) is low, or output = "ZZZZZZZZ" (high impedance) otherwise.

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY tri state IS

PORT ( ena: IN STD LOGIC;

input: IN STD LOGIC VECTOR (7 DOWNTO 0);

output: OUT STD LOGIC VECTOR (7 DOWNTO 0));

END tri state;

10 ARCHITECTURE tri state OF tri state IS

11 BEGIN

12

output <= input WHEN (ena='0') ELSE

13

(OTHERS => 'Z');

14 END tri state;

```

Figure 5.7 Simulation results of example 5.3.

**Tri-state Buffer**

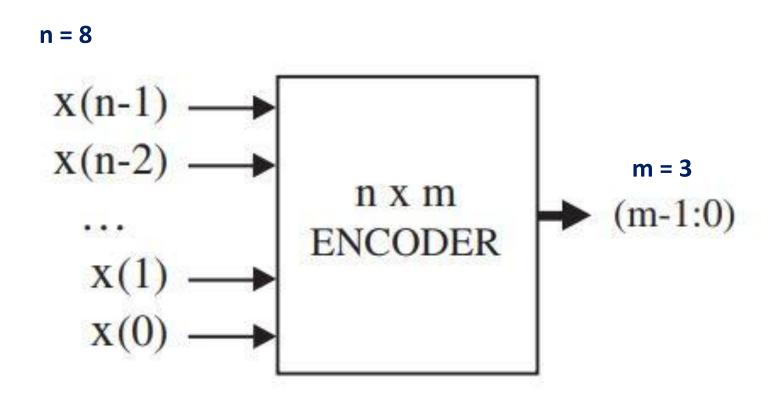

Figure 5.8 Encoder of example 5.4.

```

---- Solution 1: with WHEN/ELSE -----

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY encoder IS

PORT ( x: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

6

y: OUT STD LOGIC VECTOR (2 DOWNTO 0));

END encoder;

10 ARCHITECTURE encoder1 OF encoder IS

11 BEGIN

12

y <= "000" WHEN x="00000001" ELSE

13

"001" WHEN x="00000010" ELSE

14

"010" WHEN x="00000100" ELSE

15

"011" WHEN x="00001000" ELSE

16

"100" WHEN x="00010000" ELSE

17

"101" WHEN x="00100000" ELSE

18

"110" WHEN x="01000000" ELSE

"111" WHEN x="10000000" ELSE

19

20

"ZZZ";

```

END encoder1;

```

---- Solution 2: with WITH/SELECT/WHEN -----

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY encoder IS

PORT ( x: IN STD LOGIC VECTOR (7 DOWNTO 0);

y: OUT STD LOGIC VECTOR (2 DOWNTO 0));

END encoder;

10 ARCHITECTURE encoder2 OF encoder IS

11 BEGIN

12

WITH x SELECT

13

y <= "000" WHEN "00000001",

14

"001" WHEN "00000010",

15

"010" WHEN "00000100",

"011" WHEN "00001000",

16

17

"100" WHEN "00010000",

"101" WHEN "00100000",

18

19

"110" WHEN "01000000",

20

"111" WHEN "10000000",

21

"ZZZ" WHEN OTHERS;

22 END encoder2;

```

Figure 5.9

Simulation results of example 5.4.

**Encoder**

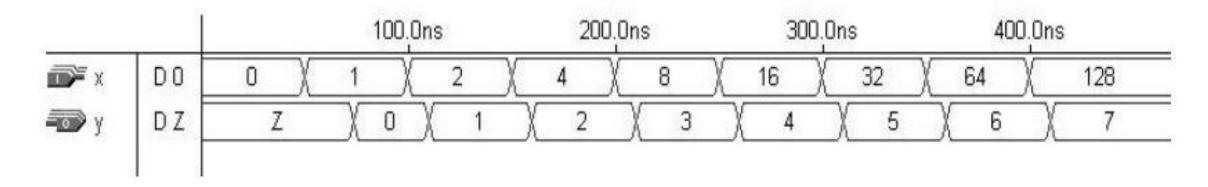

Figure: ALU (Arithmetic Logic Unit) of Example 5.5

| sel  | Operation                | Function               | Unit       |  |

|------|--------------------------|------------------------|------------|--|

| 0000 | y <= a                   | Transfer a             |            |  |

| 0001 | $y \le a+1$              | Increment a            |            |  |

| 0010 | $y \le a-1$              | Decrement a            |            |  |

| 0011 | $y \le b$                | Transfer b             | Arithmetic |  |

| 0100 | $y \le b+1$              | Increment b            |            |  |

| 0101 | $y \le b-1$              | Decrement b            |            |  |

| 0110 | $y \le a+b$              | Add a and b            |            |  |

| 0111 | $y \le a+b+cin$          | Add a and b with carry |            |  |

| 1000 | y <= NOT a               | Complement a           |            |  |

| 1001 | $y \le NOT b$            | Complement b           |            |  |

| 1010 | $y \le a \text{ AND } b$ | AND                    |            |  |

| 1011 | $y \le a OR b$           | OR                     | Logic      |  |

| 1100 | $y \le a NAND b$         | NAND                   | 25000      |  |

| 1101 | $y \le a NOR b$          | NOR                    |            |  |

| 1110 | $y \le a XOR b$          | XOR                    |            |  |

| 1111 | $y \le a XNOR b$         | XNOR                   |            |  |

**Table: ALU operation of Example 5.5**

```

LIBRARY ieee;

23

b-1 WHEN "101",

USE ieee.std logic 1164.all;

24

a+b WHEN "110",

USE ieee.std logic unsigned.all;

25

a+b+cin WHEN OTHERS;

---- Logic unit: -----

26

ENTITY ALU IS

27

WITH sel(2 DOWNTO 0) SELECT

PORT (a, b: IN STD LOGIC VECTOR (7 DOWNTO 0);

28

logic <= NOT a WHEN "000",

sel: IN STD LOGIC VECTOR (3 DOWNTO 0);

29

NOT b WHEN "001",

cin: IN STD LOGIC;

y: OUT STD LOGIC VECTOR (7 DOWNTO 0));

10

30

a AND b WHEN "010",

11 END ALU;

31

a OR b WHEN "011",

32

a NAND b WHEN "100",

13 ARCHITECTURE dataflow OF ALU IS

33

a NOR b WHEN "101",

SIGNAL arith, logic: STD LOGIC VECTOR (7 DOWNTO 0);

34

a XOR b WHEN "110",

15 BEGIN

35

NOT (a XOR b) WHEN OTHERS;

16

---- Arithmetic unit: -----

36

----- Mux: ------

17

WITH sel(2 DOWNTO 0) SELECT

WITH sel(3) SELECT

18

arith <= a WHEN "000",

y <= arith WHEN '0',

38

19

a+1 WHEN "001",

a-1 WHEN "010",

20

39

logic WHEN OTHERS;

21

b WHEN "011",

40 END dataflow;

b+1 WHEN "100",

22

```

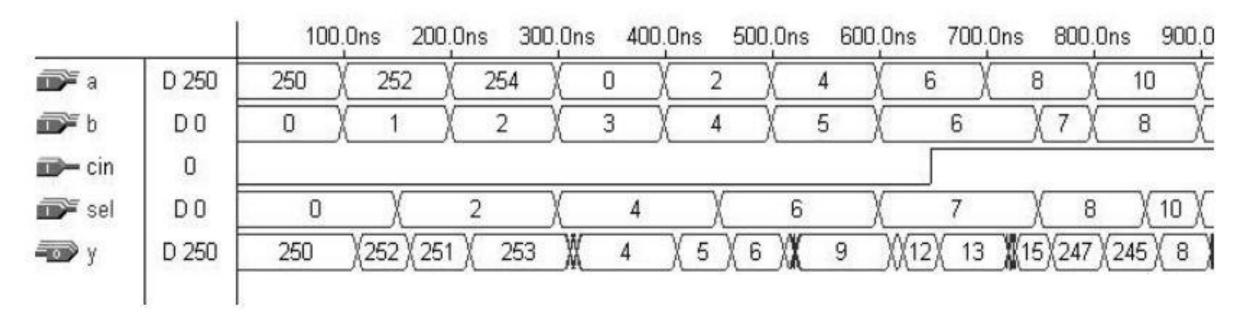

Figure 5.11 Simulation results of example 5.5.

#### **ALU**

- GENERATE is another concurrent statement (along with operators and WHEN).

- It is equivalent to the sequential statement LOOP (chapter 6) in the sense that it allows a section of code to be repeated a number of times, thus creating several instances of the same assignments.

- Its regular form is the **FOR / GENERATE** construct, with the syntax shown below. Notice that GENERATE must be labeled.

#### FOR / GENERATE:

```

label: FOR identifier IN range GENERATE

(concurrent assignments)

END GENERATE;

```

• An irregular form is also available, which uses **IF/GENERATE** (with an IF equivalent; recall that originally IF is a sequential statement). Here ELSE is not allowed. In the same way that **IF/GENERATE** can be nested inside **FOR/GENERATE** (syntax below), the opposite can also be done.

#### IF / GENERATE nested inside FOR / GENERATE:

```

label1: FOR identifier IN range GENERATE

...

label2: IF condition GENERATE

(concurrent assignments)

END GENERATE;

...

END GENERATE;

```

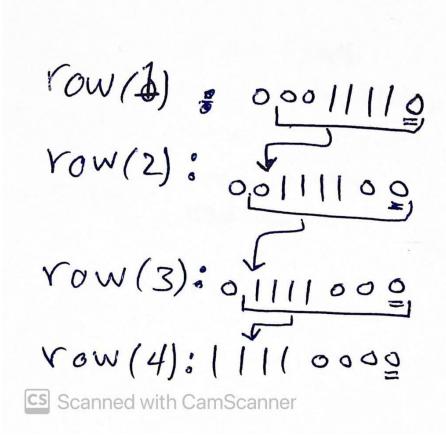

#### **Example 5.6: Vector Shifter**

```

(the original vector is underscored):

row(0): 0 0 0 0 1 1 1 1

row(1): 0 0 0 <u>1 1 1 1 0</u>

row(2): 0 0 1 1 1 1 0 0

row(3): 0 1 1 1 1 0 0 0

row(4): 1 1 1 1 0 0 0 0

```

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY shifter IS

PORT ( inp: IN STD LOGIC VECTOR (3 DOWNTO 0);

sel: IN INTEGER RANGE 0 TO 4;

outp: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END shifter;

11 ARCHITECTURE shifter OF shifter IS

12

SUBTYPE vector IS STD LOGIC VECTOR (7 DOWNTO 0);

TYPE matrix IS ARRAY (4 DOWNTO 0) OF vector;

13

14

SIGNAL row: matrix;

15 BEGIN

16

row(0) \le "0000" \& inp;

G1: FOR i IN 1 TO 4 GENERATE

17

18

row(i) \le row(i-1)(6 DOWNTO 0) & '0';

19

END GENERATE;

20

outp <= row(sel);

21 END shifter;

```

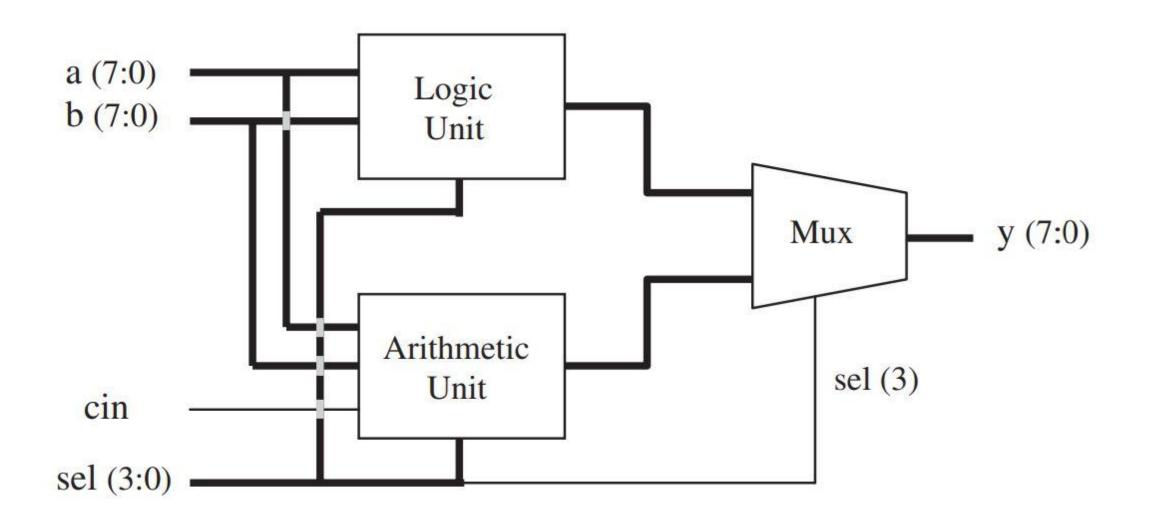

**Vector Shifter**

|              |    | 100.0ns | 200,0ns | 300.0ns | 400,0ns | 500,0ns | 600,0ns       | 700.0ns | 800.0r |

|--------------|----|---------|---------|---------|---------|---------|---------------|---------|--------|

| inp inp      | D3 |         |         |         | 3       |         |               |         |        |

| <b>a</b> sel | D0 | 0       | 1       | X       | 2       | ( 3     | X             | 4       | 5      |

| outp         | D3 | 3       | 7 6     | γ       | 12      | 24      | $\overline{}$ | 48      | X 0    |

Figure 5.12 Simulation results of example 5.6.

Simulation results are presented in figure 5.12. As can be seen, inp = "0011" (decimal 3) was applied to the circuit. The result was outp = "00000011" (decimal 3) when sel = 0 (no shift), outp = "00000110" (decimal 6) when sel = 1 (one shift to the left), outp = "00001100" (decimal 12) when sel = 2 (two shifts to the left), and so on.

# Assignments

• The assignments will be attached in your class room.

### **End of lecture 4**

Any Questions?