# Integrated Circuits Design by FPGA

م.م. أحمد مؤيد عبدالحسين جامعة الفرات الأوسط التقنية / الكلية التقنية الهندسية / نجف

## **VHDL Sequential Code**

# **Objectives of this Lecture**

- To understand what is the Sequential VHDL code.

- Also, this lecture is very important, for it allows a better understanding of where the parallel VHDL code or sequential VHDL code, as well as the consequences of using one or the other.

# **Contents of this Lecture**

- Introduction about Sequential VHDL code.

- Sequential VHDL code inside **Processes**

- Sequential VHDL code inside Processes | IF

- Sequential VHDL code inside Processes\ WAIT

- Sequential VHDL code inside Processes <u>CASE</u>

# **Introduction about Sequential VHDL code**

• VHDL code can be concurrent (parallel) or sequential.

• As mentioned in lecture 4, VHDL code is inherently concurrent.

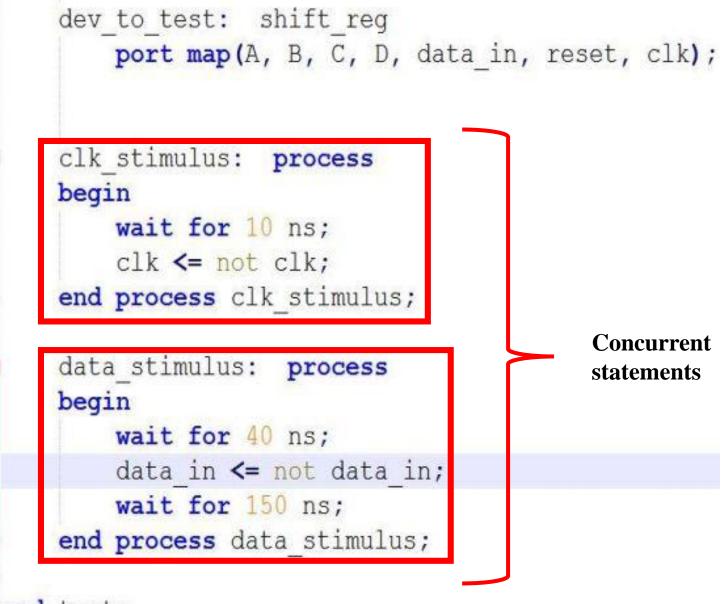

• **PROCESSES**, **FUNCTIONS**, and **PROCEDURES** are the only sections of code that are executed sequentially. However, as a whole, any of these blocks is still concurrent with any other statements placed outside it .

# **Introduction about Sequential VHDL code**

# **Introduction about Sequential VHDL code**

- The <u>statements</u> discussed in this section are all sequential, that is, allowed only <u>inside</u> **PROCESSES**, **FUNCTIONS**, or **PROCEDURES**. They are: <u>**IF**</u>, **WAIT**, **CASE**, and **LOOP**.

- VARIABLES are also restricted to be used in sequential code only (that is, inside a PROCESS, FUNCTION, or PROCEDURE).

- A PROCESS is a sequential section of VHDL code. It is characterized by the presence of **IF**, **WAIT**, **CASE**, or **LOOP**, and by a sensitivity list (except when WAIT is used).

- A PROCESS must be installed in the main code, and is executed every time a signal in the **sensitivity list changes** (or **the condition related to WAIT is fulfilled**). Its syntax is shown below.

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

#### **IF** structure

```

IF conditions THEN assignments;

ELSIF conditions THEN assignments;

...

ELSE assignments;

END IF;

```

Example 6.1

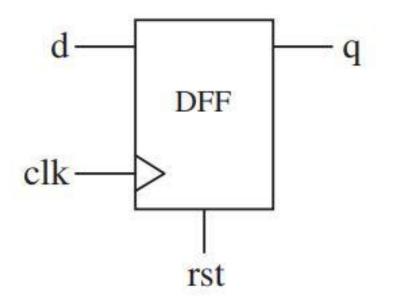

Figure 6.1 DFF with asynchronous reset of example 6.1.

```

2

LIBRARY ieee;

USE ieee.std_logic_1164.all;

3

4

ENTITY dff IS

5

PORT (d, clk, rst: IN STD LOGIC;

6

7

q: OUT STD LOGIC);

8

END dff;

-------

9

10 ARCHITECTURE behavior OF dff IS

11 BEGIN

12

PROCESS (clk, rst)

13

BEGIN

14 IF (rst='1') THEN

15

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

16

17

q <= d;

18

END IF;

19

END PROCESS;

END behavior;

20

```

- -

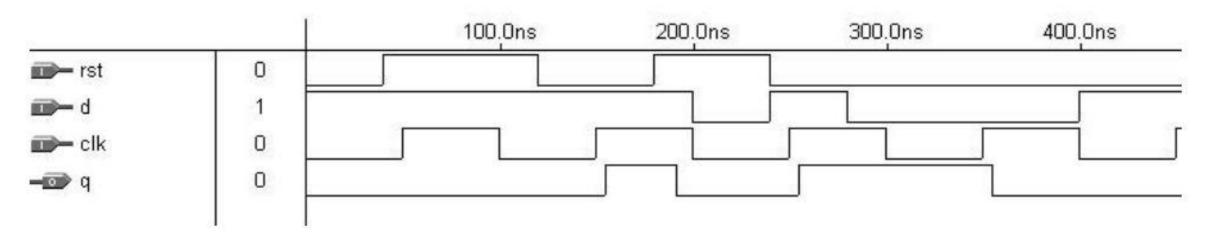

Figure 6.2 Simulation results of example 6.1.

**DFF : D Flip Flop**

Example 6.2

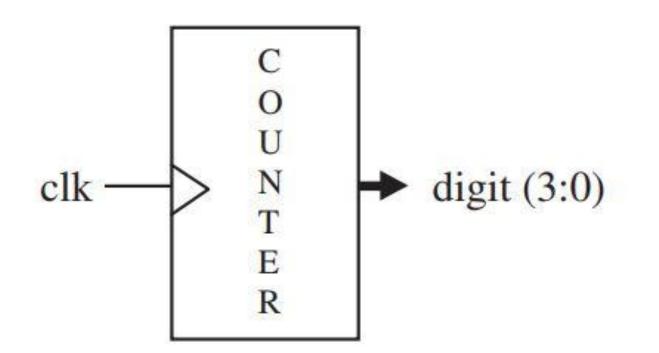

Figure 6.3 Counter of example 6.2.

```

LIBRARY ieee;

2

USE ieee.std logic 1164.all;

3

4

_____

5

ENTITY counter IS

PORT (clk : IN STD LOGIC;

6

digit : OUT INTEGER RANGE 0 TO 9);

7

8

END counter;

9

10 ARCHITECTURE counter OF counter IS

11 BEGIN

12

count: PROCESS(clk)

VARIABLE temp : INTEGER RANGE 0 TO 10;

13

14

BEGIN

15

IF (clk'EVENT AND clk='1') THEN

16

temp := temp + 1;

17

IF (temp=10) THEN temp := 0;

18

END IF;

19

END IF;

20

digit <= temp;

21

END PROCESS count;

22 END counter;

```

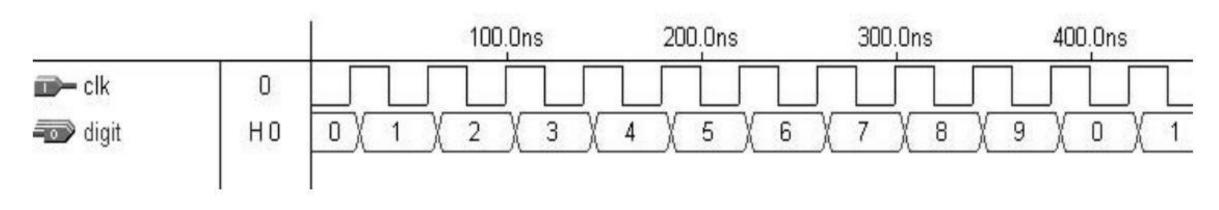

**Figure 6.4** Simulation results of example 6.2.

#### Counter

```

L-- Begin Architecture

26

-- Library's

Example 6.3: shift register

27

begin

library IEEE;

28

29

-- Signal Assignments

use IEEE.STD LOGIC 1164.ALL;

30

A \leq A reg;

use IEEE.numeric std.all;

31

B \ll B reg;

5

32

C \ll C reg;

33

D <= D reg;

-- Entity Declaration

34

entity Shift Reg is

35

-- Process that is used to shift values

36

Eport (

** HINT **

-- (We want this process to be evaluated

37

-- single bit in register

9

: out std logic;

A

38

-- on every clock cycle)

: out std logic;

-- single bit in register

10

В

39

reg process: process(clk)

С

40

: out std logic;

-- single bit in register

begin

11

41

日日

if(rising edge(clk)) then

12

: out std logic;

-- single bit in register

D

42

if(reset = '1') then

13

data in

: in std logic; -- data input (1 or 0)

43

A reg <= '0';

44

B reg <= '0';

14

reset

: in std logic;

-- when this signal goes high clea:

45

C reg <= '0';

15

-- all bit values on a clock cycle

46

D reg <= '0';

47

16

clk

: in std logic);

-- input clock

Ē

else

48

** HINT **

17

end Shift Reg;

49

-- This is where the shifting actually occurs

18

50

-- depending on how you code this, you can have

51

-- a shift right or shift left register

19

-- Architecture Body

52

A reg <= data in;

□architecture behavior of Shift Reg is

20

53

B reg <= A reg;

54

21

C reg <= B reg;

55

D reg <= C reg;

-- Defined Signals used in Architecture

22

56

end if;

signal A reg, B_reg : std_logic := '0';

23

end if;

57

58

end process reg process;

signal C req, D req : std logic := '0';

24

59

end behavior:

0.5

```

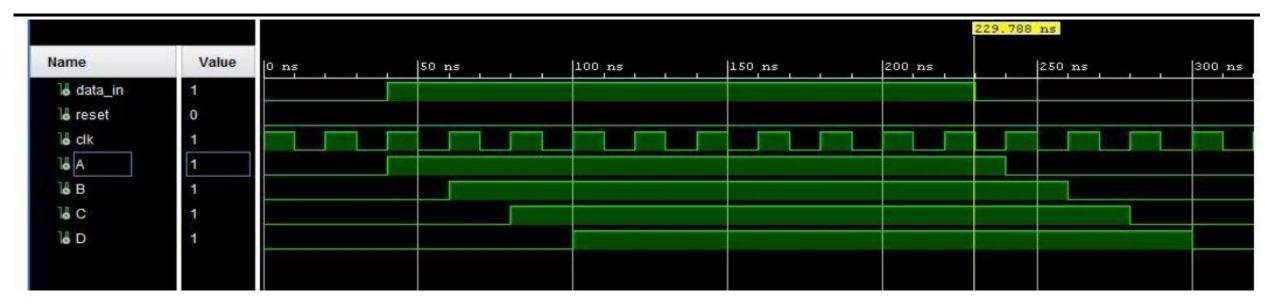

#### **Example 6.3: shift register**

(there are three forms of WAIT) is shown below.

WAIT UNTIL signal\_condition;

WAIT ON signall [, signal2, ... ];

WAIT FOR time;

Example: 8-bit register with synchronous reset.

PROCESS -- no sensitivity list BEGIN

WAIT UNTIL (clk'EVENT AND clk='1'); IF (rst='1') THEN output <= "00000000"; ELSIF (clk'EVENT AND clk='1') THEN output <= input; END IF; END PROCESS;

Example: 8-bit register with asynchronous reset.

```

PROCESS

BEGIN

WAIT ON clk, rst;

IF (rst='1') THEN

output <= "00000000";

ELSIF (clk'EVENT AND clk='1') THEN

output <= input;

END IF;

END PROCESS;

```

• Finally, **WAIT FOR** is intended for simulation only (waveform generation for testbenches). Example:

#### WAIT FOR 5ns;

• CASE is another statement intended exclusively for sequential code (along with IF, LOOP, and WAIT). Its syntax is shown below:

```

CASE identifier IS

WHEN value => assignments;

WHEN value => assignments;

....

END CASE;

```

• The CASE statement (sequential) is very similar to WHEN (combinational).

Note : Parallel = Concurrent = Combinational

- Here too all permutations must be tested.

- However, **CASE** allows multiple assignments for each test condition (as shown in the previous slide), while **WHEN** allows only one.

- Like in the case of **WHEN** (lecture 4), here too "**WHEN value**" can take up three forms:

WHEN value WHEN value1 to value2

WHEN value1 | value2 |...

- -- single value

- -- range, for enumerated data types

-- only

- -- value1 or value2 or ...

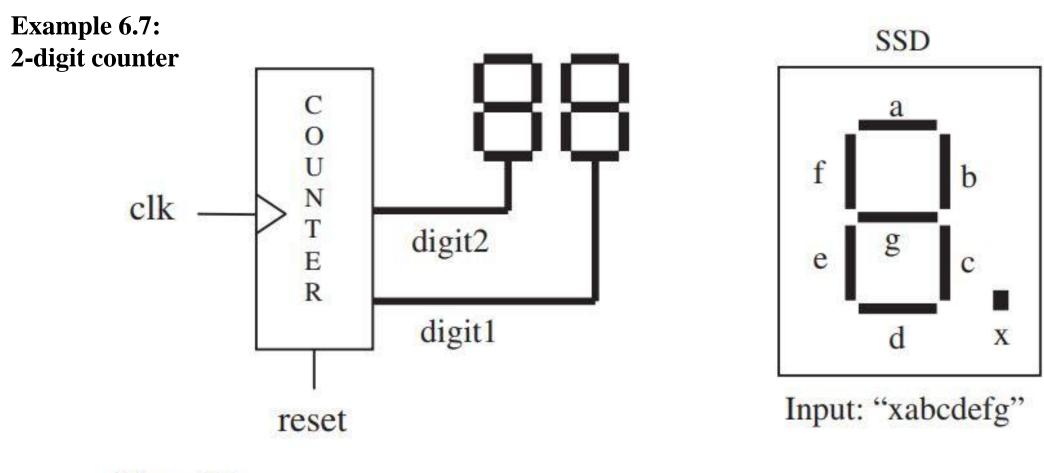

Figure 6.7 2-digit counter of example 6.7.

```

LIBRARY ieee;

2

USE ieee.std logic 1164.all;

3

------

ENTITY counter IS

5

PORT (clk, reset : IN STD LOGIC;

6

digit1, digit2 : OUT STD_LOGIC_VECTOR (6 DOWNTO 0));

7

8

END counter;

_____

9

10 ARCHITECTURE counter OF counter IS

11 BEGIN

PROCESS(clk, reset)

12

VARIABLE temp1: INTEGER RANGE 0 TO 10;

13

VARIABLE temp2: INTEGER RANGE 0 TO 10;

14

15

BEGIN

16

---- counter: -----

17

IF (reset='1') THEN

18

temp1 := 0;

19

temp2 := 0;

20

ELSIF (clk'EVENT AND clk='1') THEN

21

temp1 := temp1 + 1;

22

IF (temp1=10) THEN

23

temp1 := 0;

24

temp2 := temp2 + 1;

25

IF (temp2=10) THEN

temp2 := 0;

26

```

| 27 | END IF;                          |

|----|----------------------------------|

| 28 | END IF;                          |

| 29 | END IF;                          |

| 30 | BCD to SSD conversion:           |

| 31 | CASE temp1 IS                    |

| 32 | WHEN 0 => digit1 <= "1111110";7E |

| 33 | WHEN 1 => digit1 <= "0110000";30 |

| 34 | WHEN 2 => digit1 <= "1101101";6D |

| 35 | WHEN 3 => digit1 <= "1111001";79 |

| 36 | WHEN 4 => digit1 <= "0110011";33 |

| 37 | WHEN 5 => digit1 <= "1011011";5B |

| 38 | WHEN 6 => digit1 <= "1011111";5F |

| 39 | WHEN 7 => digit1 <= "1110000";70 |

| 40 | WHEN 8 => digit1 <= "1111111";7F |

| 41 | WHEN 9 => digit1 <= "1111011";7B |

| 42 | WHEN OTHERS => NULL;             |

| 43 | END CASE;                        |

| 44 | CASE temp2 IS                    |

| 45 | WHEN 0 => digit2 <= "1111110";7E |

| 46 | WHEN 1 => digit2 <= "0110000";30 |

| 47 | WHEN 2 => digit2 <= "1101101";6D |

| 48 | WHEN 3 => digit2 <= "1111001";79 |

| 49 | WHEN 4 => digit2 <= "0110011";33 |

| 50 | WHEN 5 => digit2 <= "1011011";5B |

| 51 | WHEN 6 => digit2 <= "1011111";5F |

| 52 | WHEN 7 => digit2 <= "1110000";70 |

| 53 | WHEN 8 => digit2 <= "1111111";7F |

| 54 | WHEN 9 => digit2 <= "1111011";7B |

| 55 | WHEN OTHERS => NULL;             |

| 56 | END CASE;                        |

| 57 | END PROCESS;                     |

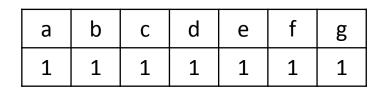

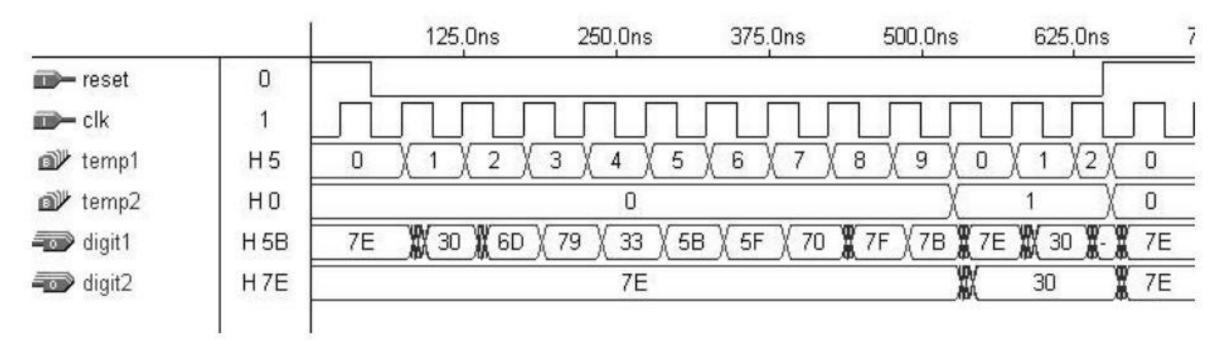

Figure 6.8 Simulation results of example 6.7.

2-digit counter

- Design the same **DFF** of example 6.1 by using **WAIT** statement.

- Design the same progressive 1-digit decimal **counter** of example 6.2 by using **WAIT** statement.

# **End of lecture 5**

**Any Questions ?**