# Integrated Circuits Design by FPGA

مم مم أحمد مؤيد عبدالحسين جامعة الفرات الأوسط التقنية / الكلية التقنية الهندسية / نجف

# Lecture 8

#### Finite State Machines (FSM)

## Objectives of this Lecture

- To define the term **Finite State Machines** (**FSM**). And to recognize its principles.

- To implement digital systems using **FSM** method.

- To indicate the difference between FSM style #1 and FSM style #2

# Contents of this Lecture

• **FSM** introduction.

• **FSM** style #1

• **FSM** can be very helpful in the design of certain types of systems, particularly those whose tasks form a well-defined sequence (digital controllers, for example).

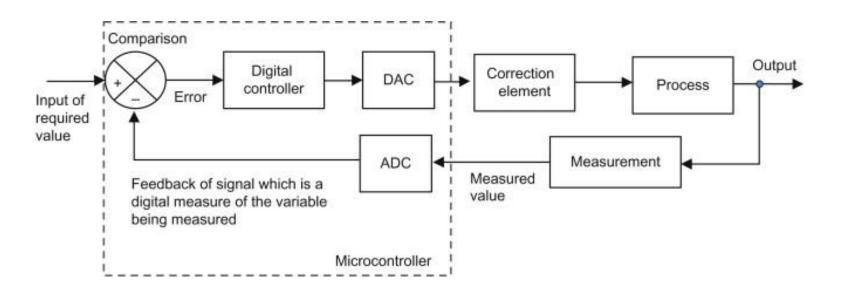

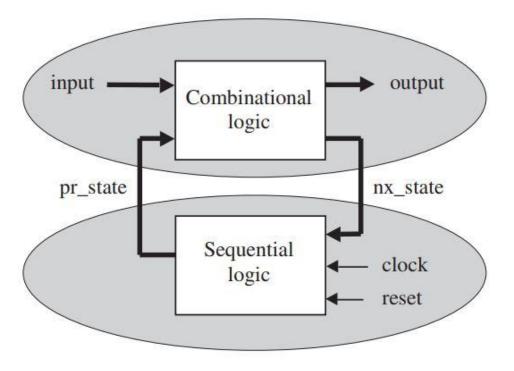

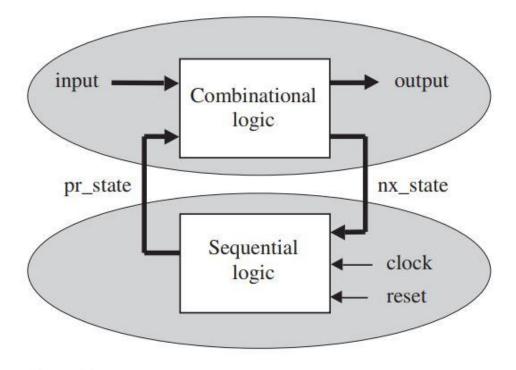

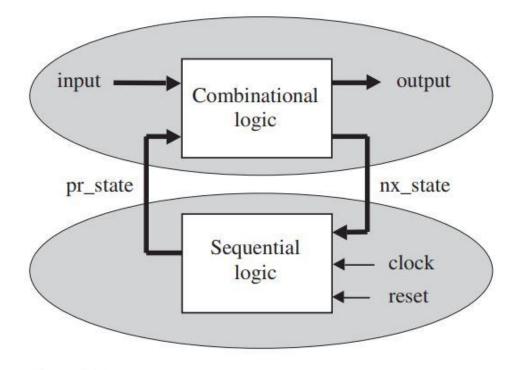

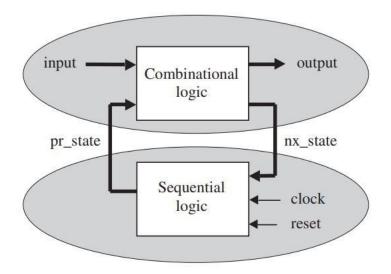

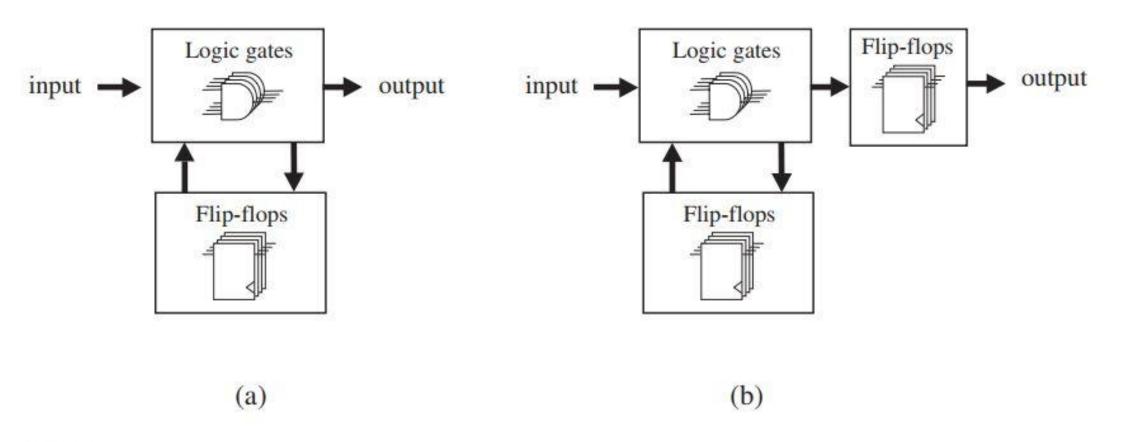

• Figure 8.1 shows the block diagram of a single-phase state machine. As indicated in the figure, the lower section contains the sequential logic (flip-flops), while the upper section contains the combinational logic (parallel VHDL).

Figure 8.1 Mealy (Moore) state machine diagram.

• The combinational (upper) section has two inputs, being one **pr\_state** (present state) and the other the external input proper. It has also two outputs, **nx\_state** (next state) and the external output proper.

Figure 8.1 Mealy (Moore) state machine diagram.

• The sequential (lower) section has three inputs (clock, reset, and nx\_state), and one output (pr\_state). Since all flip-flops are in this part of the system, clock and reset must be connected to it.

Figure 8.1 Mealy (Moore) state machine diagram.

- From a VHDL perspective, it is clear that the lower part, being sequential, will require a PROCESS, while the upper part, being combinational, will not.

- However, it is also possible to use PROCESS inside the upper part to implement combinational (parallel) design.

Figure 8.1 Mealy (Moore) state machine diagram.

- One important aspect related to the **FSM** approach is that, though any sequential circuit can in principle be modeled as a state machine, this is not always advantageous. The reason is that the code might become longer, more complex, and more error prone than in a conventional approach. This is often the case with simple registered circuits, like counters.

- The **FSM** approach is advisable in systems whose tasks constitute a well structured list so all states <u>can be easily enumerated</u>. That is, in a typical state machine implementation, we will encounter, at the beginning of the ARCHITECTURE, a user-defined enumerated data type, containing <u>a list of all possible system states</u>.

Counter Example

• **FSM** method could be used to implement a counter circuit. The problem with the **FSM** is that when the number of states is large it becomes cumbersome to enumerate them all, a problem easily avoided using the LOOP statement or other conventional approaches.

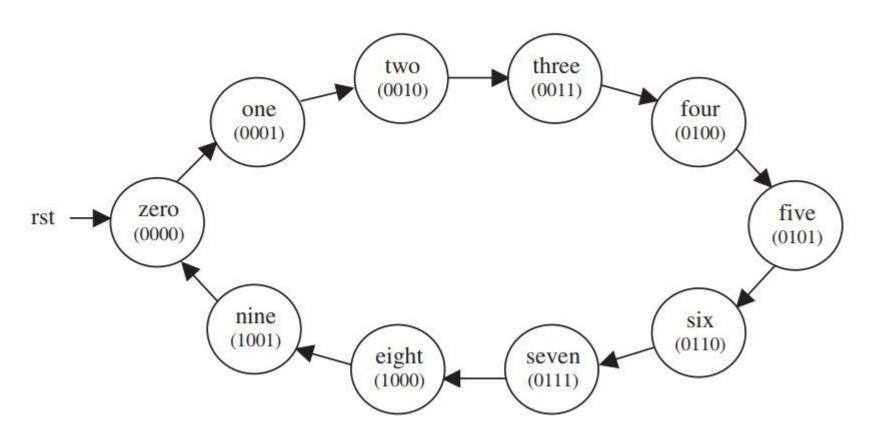

• The state diagram of a 0-to-9 circular counter is shown in figure 8.2. The states were called **zero**, **one**, . . . , **nine**, each name corresponding to the decimal value of the output.

Figure 8.2 States diagram of example 8.1.

```

LIBRARY ieee;

2

USE ieee.std_logic_1164.all;

3

4

5

ENTITY counter IS

PORT ( clk, rst: IN STD LOGIC;

count: OUT STD LOGIC VECTOR (3 DOWNTO 0));

END counter;

10 ARCHITECTURE state machine OF counter IS

11

TYPE state IS (zero, one, two, three, four,

12

five, six, seven, eight, nine);

13

SIGNAL pr state, nx state: state;

14 BEGIN

----- Lower section: -----

15

16

PROCESS (rst, clk)

17

BEGIN

18

IF (rst='1') THEN

19

pr state <= zero;

20

ELSIF (clk'EVENT AND clk='1') THEN

21

pr state <= nx state;</pre>

22

END IF;

23

END PROCESS;

```

```

24

----- Upper section:

25

PROCESS (pr state)

26

BEGIN

27

CASE pr state IS

28

WHEN zero =>

29

count <= "0000";

30

nx state <= one;

31

WHEN one =>

32

count <= "0001";

33

nx state <= two;

34

WHEN two =>

35

count <= "0010";

36

nx state <= three;

37

WHEN three =>

38

count <= "0011";

39

nx state <= four;

WHEN four =>

40

41

count <= "0100";

nx state <= five;

42

```

```

43

WHEN five =>

44

count <= "0101";

45

nx state <= six;

WHEN six =>

46

47

count <= "0110";

nx state <= seven;

48

49

WHEN seven =>

count <= "0111";

50

nx state <= eight;

51

52

WHEN eight =>

53

count <= "1000";

54

nx state <= nine;

55

WHEN nine =>

56

count <= "1001";

nx state <= zero;

57

58

END CASE;

END PROCESS;

59

60 END state machine;

```

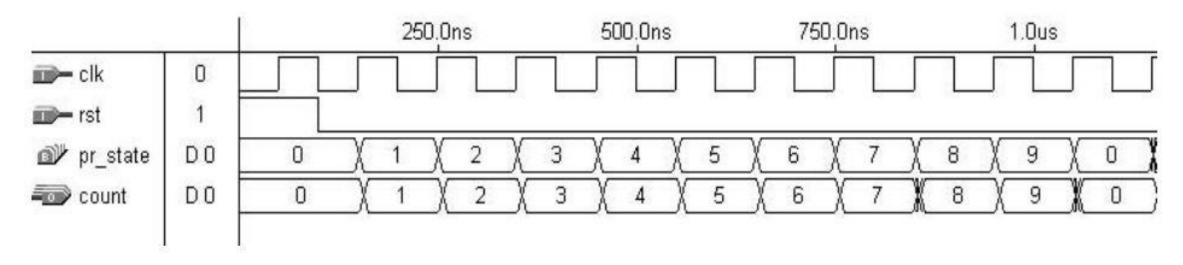

Figure 8.3 Simulation results of example 8.1.

#### **Example 8.1 Counter**

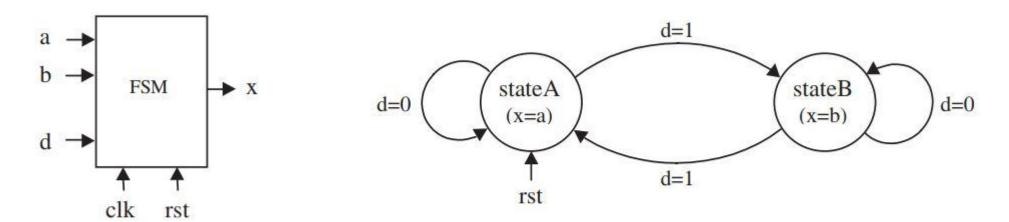

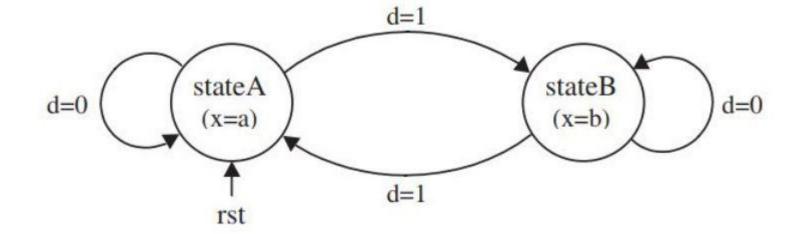

#### Example 8.2 : Simple FSM #1

Figure 8.4

State machine of example 8.2

```

ENTITY simple fsm IS

PORT ( a, b, d, clk, rst: IN BIT;

x: OUT BIT);

END simple fsm;

ARCHITECTURE simple fsm OF simple fsm IS

TYPE state IS (stateA, stateB);

SIGNAL pr state, nx state: state;

10 BEGIN

---- Lower section: -----

11

12

PROCESS (rst, clk)

13

BEGIN

14

IF (rst='1') THEN

15

pr state <= stateA;

ELSIF (clk'EVENT AND clk='1') THEN

16

17

pr state <= nx state;

18

END IF;

19

END PROCESS;

```

```

20

----- Upper section: -----

21

PROCESS (a, b, d, pr_state)

22

BEGIN

23

CASE pr state IS

24

WHEN stateA =>

25

x \leq a;

26

IF (d='1') THEN nx state <= stateB;</pre>

27

ELSE nx state <= stateA;</pre>

28

END IF;

29

WHEN stateB =>

30

x \le b;

31

IF (d='1') THEN nx state <= stateA;</pre>

32

ELSE nx state <= stateB;</pre>

33

END IF;

34

END CASE;

35

END PROCESS;

36 END simple_fsm;

```

Figure 8.6

Circuit diagrams for (a) Design Style #1 and (b) Design Style #2.

The only difference is?

#### Example 8.3 : Simple FSM #2

```

ENTITY simple fsm IS

PORT (a, b, d, clk, rst: IN BIT;

x: OUT BIT);

END simple fsm;

ARCHITECTURE simple fsm OF simple fsm IS

TYPE state IS (stateA, stateB);

SIGNAL pr state, nx state: state;

10

SIGNAL temp: BIT;

11 BEGIN

---- Lower section: -----

12

13

PROCESS (rst, clk)

14

BEGIN

15

IF (rst='1') THEN

16

pr state <= stateA;</pre>

17

ELSIF (clk'EVENT AND clk='1') THEN

18

x <= temp;

19

pr state <= nx state;

20

END IF;

21

END PROCESS;

```

```

----- Upper section: -----

22

23

PROCESS (a, b, d, pr state)

24

BEGIN

25

CASE pr state IS

26

WHEN stateA =>

27

temp <= a;

28

IF (d='1') THEN nx state <= stateB;</pre>

29

ELSE nx state <= stateA;</pre>

30

END IF;

31

WHEN stateB =>

temp <= b;

32

33

IF (d='1') THEN nx state <= stateA;</pre>

34

ELSE nx state <= stateB;</pre>

35

END IF;

36

END CASE;

37

END PROCESS;

38 END simple fsm;

```

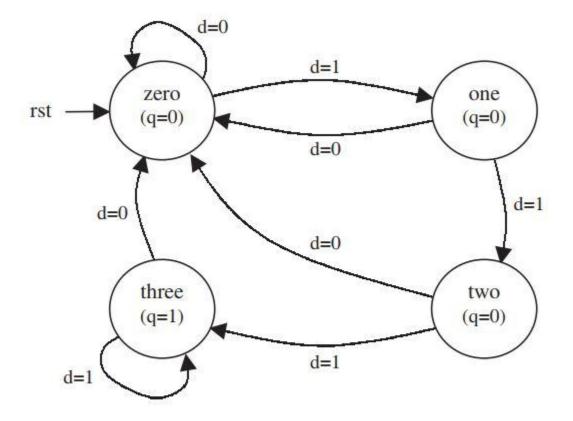

#### **Example 8.4: String detector**

Figure 8.8 States diagram for example 8.4.

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

------

ENTITY string detector IS

PORT ( d, clk, rst: IN BIT;

q: OUT BIT);

END string detector;

10 ARCHITECTURE my arch OF string detector IS

11

TYPE state IS (zero, one, two, three);

12

SIGNAL pr state, nx state: state;

13 BEGIN

14

---- Lower section: -----

15

PROCESS (rst, clk)

16

BEGIN

17

IF (rst='1') THEN

18

pr state <= zero;

19

ELSIF (clk'EVENT AND clk='1') THEN

20

pr state <= nx state;

21

END IF;

22

END PROCESS;

```

```

23

----- Upper section: -----

24

PROCESS (d, pr state)

25

BEGIN

26

CASE pr state IS

27

WHEN zero =>

28

q <= '0';

29

IF (d='1') THEN nx state <= one;</pre>

30

ELSE nx state <= zero;

31

END IF;

32

WHEN one =>

33

q <= '0';

34

IF (d='1') THEN nx state <= two;</pre>

35

ELSE nx state <= zero;

36

END IF;

37

WHEN two =>

38

q <= '0';

39

IF (d='1') THEN nx state <= three;</pre>

40

ELSE nx state <= zero;

41

END IF;

```

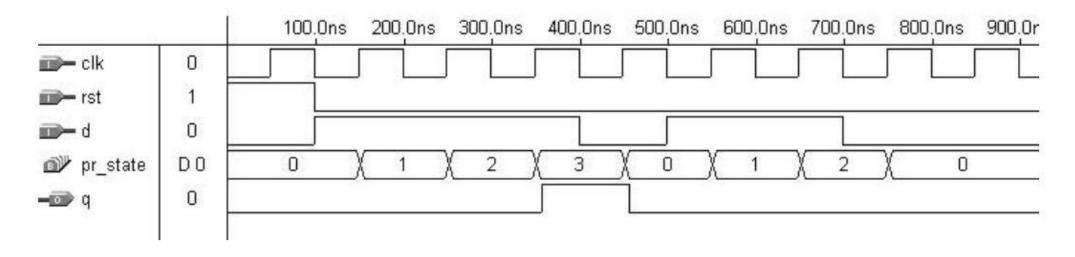

Figure 8.9 Simulation results of example 8.4.

**Example 8.4: String detector**

# Assignments

• The assignments will be attached to your class room.

# End of lecture 8

Any Questions?